- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45331 > MK51N512CLQ100 (FREESCALE SEMICONDUCTOR INC) 32-BIT, FLASH, 100 MHz, RISC MICROCONTROLLER, PQFP144 PDF資料下載

參數(shù)資料

| 型號(hào): | MK51N512CLQ100 |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, FLASH, 100 MHz, RISC MICROCONTROLLER, PQFP144 |

| 封裝: | 20 X 20 MM, LQFP-144 |

| 文件頁(yè)數(shù): | 20/74頁(yè) |

| 文件大?。?/td> | 1831K |

| 代理商: | MK51N512CLQ100 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)當(dāng)前第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)

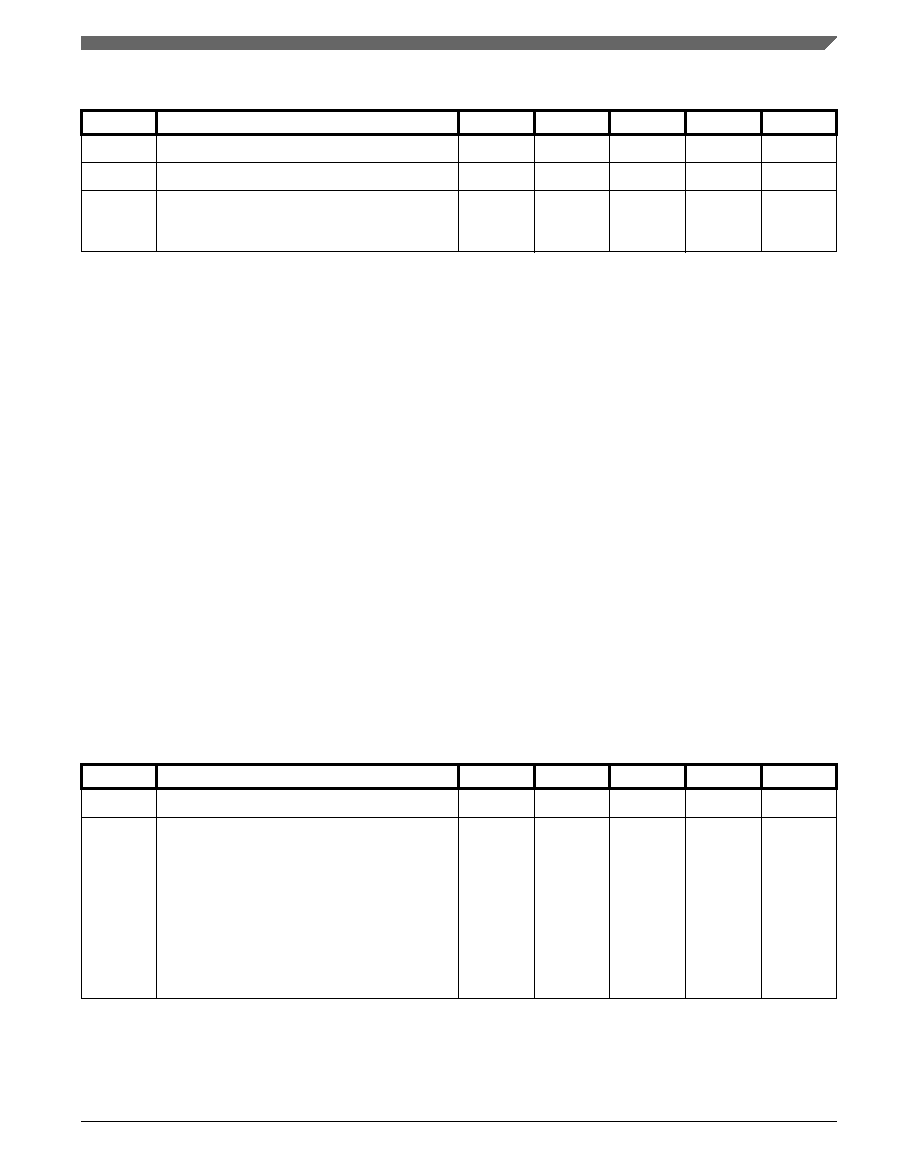

Table 13. MCG specifications (continued)

Symbol

Description

Min.

Typ.

Max.

Unit

Notes

Dlock

Lock entry frequency tolerance

± 1.49

—

± 2.98

%

Dunl

Lock exit frequency tolerance

± 4.47

—

± 5.97

%

tpll_lock

Lock detector detection time

—

0.15 +

1075(1/

fpll_ref)

ms

1. This parameter is measured with the internal reference (slow clock) being used as a reference to the FLL (FEI clock

mode).

2. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32=0.

3. The resulting system clock frequencies should not exceed their maximum specified values. The DCO frequency deviation

(

Δfdco_t) over voltage and temperature should be considered.

4. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32=1.

5. The resulting clock frequency must not exceed the maximum specified clock frequency of the device.

6. This specification was obtained at TBD frequency.

7. This specification applies to any time the FLL reference source or reference divider is changed, trim value is changed,

DMX32 bit is changed, DRS bits are changed, or changing from FLL disabled (BLPE, BLPI) to FLL enabled (FEI, FEE,

FBE, FBI). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

8. Excludes any oscillator currents that are also consuming power while PLL is in operation.

9. This specification was obtained using a Freescale developed PCB. PLL jitter is dependent on the noise characteristics of

each PCB and results will vary.

10. This specification was obtained at internal frequency of TBD.

11. This specification applies to any time the PLL VCO divider or reference divider is changed, or changing from PLL disabled

(BLPE, BLPI) to PLL enabled (PBE, PEE). If a crystal/resonator is being used as the reference, this specification assumes

it is already running.

6.3.2 Oscillator electrical specifications

This section provides the electrical characteristics of the module.

6.3.2.1 Oscillator DC electrical specifications

Table 14. Oscillator DC electrical specifications

Symbol

Description

Min.

Typ.

Max.

Unit

Notes

VDD

Supply voltage

1.71

—

3.6

V

IDDOSC

Supply current — low-power mode (HGO=0)

32 kHz

4 MHz

8 MHz

16 MHz

24 MHz

32 MHz

—

500

200

300

700

1.2

1.5

—

nA

μA

mA

Table continues on the next page...

Peripheral operating requirements and behaviors

K51 Sub-Family Data Sheet Data Sheet, Rev. 4, 3/2011.

Freescale Semiconductor, Inc.

Preliminary

27

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MK51N256CMD100 | 32-BIT, FLASH, 100 MHz, RISC MICROCONTROLLER, PBGA144 |

| MK51N512CMC100 | 32-BIT, FLASH, 100 MHz, RISC MICROCONTROLLER, PBGA121 |

| MK51X256CMC100R | 32-BIT, FLASH, 100 MHz, RISC MICROCONTROLLER, PBGA121 |

| MK51X256CLK100 | 32-BIT, FLASH, 100 MHz, RISC MICROCONTROLLER, PQFP80 |

| MK51X256CMB100R | 32-BIT, FLASH, 100 MHz, RISC MICROCONTROLLER, PBGA81 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MK51N512CMC100 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Up to 100 MHz ARM Cortex-M4 core with DSP instructions delivering 1.25 Dhrystone MIPS per MHz |

| MK51N512CMD100 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Up to 100 MHz ARM Cortex-M4 core with DSP instructions delivering 1.25 Dhrystone MIPS per MHz |

| MK51R1F | 制造商:Ohmite Mfg Co 功能描述: |

| MK51X256CLK100 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Up to 100 MHz ARM Cortex-M4 core with DSP instructions delivering 1.25 Dhrystone MIPS per MHz |

| MK51X256CLL100 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Up to 100 MHz ARM Cortex-M4 core with DSP instructions delivering 1.25 Dhrystone MIPS per MHz |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。