- 您現(xiàn)在的位置:買賣IC網 > PDF目錄45317 > MD83C154CXXX-16P883D (TEMIC SEMICONDUCTORS) 8-BIT, MROM, 16 MHz, MICROCONTROLLER, CDIP40 PDF資料下載

參數(shù)資料

| 型號: | MD83C154CXXX-16P883D |

| 廠商: | TEMIC SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, CDIP40 |

| 文件頁數(shù): | 73/242頁 |

| 文件大?。?/td> | 61013K |

| 代理商: | MD83C154CXXX-16P883D |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁當前第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁第219頁第220頁第221頁第222頁第223頁第224頁第225頁第226頁第227頁第228頁第229頁第230頁第231頁第232頁第233頁第234頁第235頁第236頁第237頁第238頁第239頁第240頁第241頁第242頁

164

ATmega165A/PA/325A/PA/3250A/PA/645A/P/6450A/P [DATASHEET]

8285E–AVR–02/2013

20.7.7

Flushing the Receive Buffer

The receiver buffer FIFO will be flushed when the Receiver is disabled, i.e., the buffer will be emptied of its con-

tents. Unread data will be lost. If the buffer has to be flushed during normal operation, due to for instance an error

condition, read the UDRn I/O location until the RXCn Flag is cleared. The following code example shows how to

flush the receive buffer.

Note:

20.8

Asynchronous Data Reception

The USART includes a clock recovery and a data recovery unit for handling asynchronous data reception. The

clock recovery logic is used for synchronizing the internally generated baud rate clock to the incoming asynchro-

nous serial frames at the RxD pin. The data recovery logic samples and low pass filters each incoming bit, thereby

improving the noise immunity of the Receiver. The asynchronous reception operational range depends on the

accuracy of the internal baud rate clock, the rate of the incoming frames, and the frame size in number of bits.

20.8.1

Asynchronous Clock Recovery

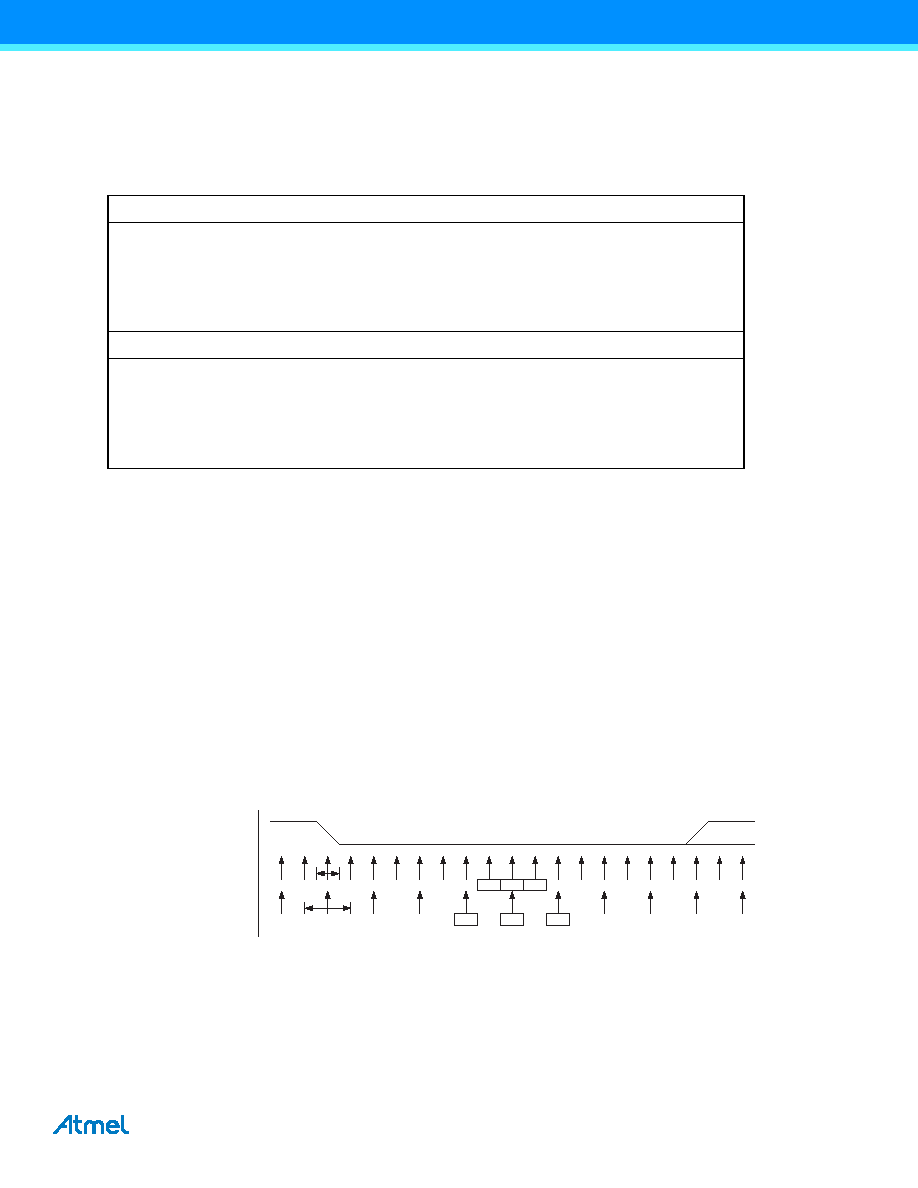

The clock recovery logic synchronizes internal clock to the incoming serial frames. Figure 20-5 illustrates the sam-

pling process of the start bit of an incoming frame. The sample rate is 16 times the baud rate for Normal mode, and

eight times the baud rate for Double Speed mode. The horizontal arrows illustrate the synchronization variation

due to the sampling process. Note the larger time variation when using the Double Speed mode (U2Xn = 1) of

operation. Samples denoted zero are samples done when the RxD line is idle (i.e., no communication activity).

Figure 20-5. Start Bit sampling.

When the clock recovery logic detects a high (idle) to low (start) transition on the RxD line, the start bit detection

sequence is initiated. Let sample 1 denote the first zero-sample as shown in the figure. The clock recovery logic

then uses samples 8, 9, and 10 for Normal mode, and samples 4, 5, and 6 for Double Speed mode (indicated with

sample numbers inside boxes on the figure), to decide if a valid start bit is received. If two or more of these three

samples have logical high levels (the majority wins), the start bit is rejected as a noise spike and the Receiver

Assembly code example

USART_Flush:

sbis

UCSR0A, RXC0

ret

in

r16, UDR0

rjmp

USART_Flush

C code example

void

USART_Flush( void )

{

unsigned char

dummy;

while

( UCSR0A & (1<<RXC0) ) dummy = UDR0;

}

12

34

56

7

8

9

10

11

12

13

14

15

16

12

START

IDLE

0

BIT 0

3

123

4

5

678

12

0

RxD

Sample

(U2X = 0)

Sample

(U2X = 1)

相關PDF資料 |

PDF描述 |

|---|---|

| MR83C154CXXX-L16P883 | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, CQCC44 |

| MR83C154TXXX-L16P883D | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, CQCC44 |

| MQ83C154XXX-20/883 | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, CQFP44 |

| MR80C154-25/883D | 8-BIT, 25 MHz, MICROCONTROLLER, CQCC44 |

| MQ83C154XXX-30P883D | 8-BIT, MROM, 30 MHz, MICROCONTROLLER, CQFP44 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MD83C154-L16 | 制造商:TEMIC 制造商全稱:TEMIC Semiconductors 功能描述:CMOS 0 to 36 MHz Single Chip 8-bit Microcontroller |

| MD83C154T-12 | 制造商:TEMIC 制造商全稱:TEMIC Semiconductors 功能描述:CMOS 0 to 36 MHz Single Chip 8-bit Microcontroller |

| MD83C154T-16 | 制造商:TEMIC 制造商全稱:TEMIC Semiconductors 功能描述:CMOS 0 to 36 MHz Single Chip 8-bit Microcontroller |

| MD83C154T-20 | 制造商:TEMIC 制造商全稱:TEMIC Semiconductors 功能描述:CMOS 0 to 36 MHz Single Chip 8-bit Microcontroller |

| MD83C154T-25 | 制造商:TEMIC 制造商全稱:TEMIC Semiconductors 功能描述:CMOS 0 to 36 MHz Single Chip 8-bit Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復。