- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382309 > MC74HC16xADR2 (ON SEMICONDUCTOR) Presettable Counters PDF資料下載

參數(shù)資料

| 型號: | MC74HC16xADR2 |

| 廠商: | ON SEMICONDUCTOR |

| 元件分類: | 通用總線功能 |

| 英文描述: | Presettable Counters |

| 中文描述: | 可預(yù)置計數(shù)器 |

| 文件頁數(shù): | 6/16頁 |

| 文件大小: | 284K |

| 代理商: | MC74HC16XADR2 |

MC74HC161A, MC74HC163A

http://onsemi.com

6

FUNCTION DESCRIPTION

The HC161A/163A are programmable 4–bit synchronous

counters that feature parallel Load, synchronous or

asynchronous Reset, a Carry Output for cascading and

count–enable controls.

The HC161A and HC163A are binary counters with

asynchronous Reset and synchronous Reset, respectively.

INPUTS

Clock (Pin 2)

The internal flip–flops toggle and the output count

advances with the rising edge of the Clock input. In addition,

control functions, such as resetting and loading occur with

the rising edge of the Clock input.

Preset Data Inputs P0, P1, P2, P3 (Pins 3, 4, 5, 6)

These are the data inputs for programmable counting.

Data on these pins may be synchronously loaded into the

internal flip–flops and appear at the counter outputs. P0 (Pin

3) is the least–significant bit and P3 (Pin 6) is the

most–significant bit.

OUTPUTS

Q0, Q1, Q2, Q3 (Pins 14, 13, 12, 11)

These are the counter outputs. Q0 (Pin 14) is the

least–significant bit and Q3 (Pin 11) is the most–significant

bit.

Ripple Carry Out (Pin 15)

When the counter is in its maximum state 1111, this output

goes high, providing an external look–ahead carry pulse that

may be used to enable successive cascaded counters. Ripple

Carry Out remains high only during the maximum count

state. The logic equation for this output is:

Ripple Carry Out = Enable T

Q0

Q1

Q2

Q3

CONTROL FUNCTIONS

Resetting

A low level on the Reset pin (Pin 1) resets the internal

flip–flops and sets the outputs (Q0 through Q3) to a low

level. The HC161A resets asynchronously, and the HC163A

resets with the rising edge of the Clock input (synchronous

reset).

Loading

With the rising edge of the Clock, a low level on Load (Pin

9) loads the data from the Preset Data input pins (P0, P1, P2,

P3) into the internal flip–flops and onto the output pins, Q0

through Q3. The count function is disabled as long as Load

is low.

Count Enable/Disable

These devices have two count–enable control pins:

Enable P (Pin 7) and Enable T (Pin 10). The devices count

when these two pins and the Load pin are high. The logic

equation is:

Count Enable = Enable P

Enable T

Load

The count is either enabled or disabled by the control

inputs according to Table 1. In general, Enable P is a

count–enable control: Enable T is both a count–enable and

a Ripple–Carry Output control.

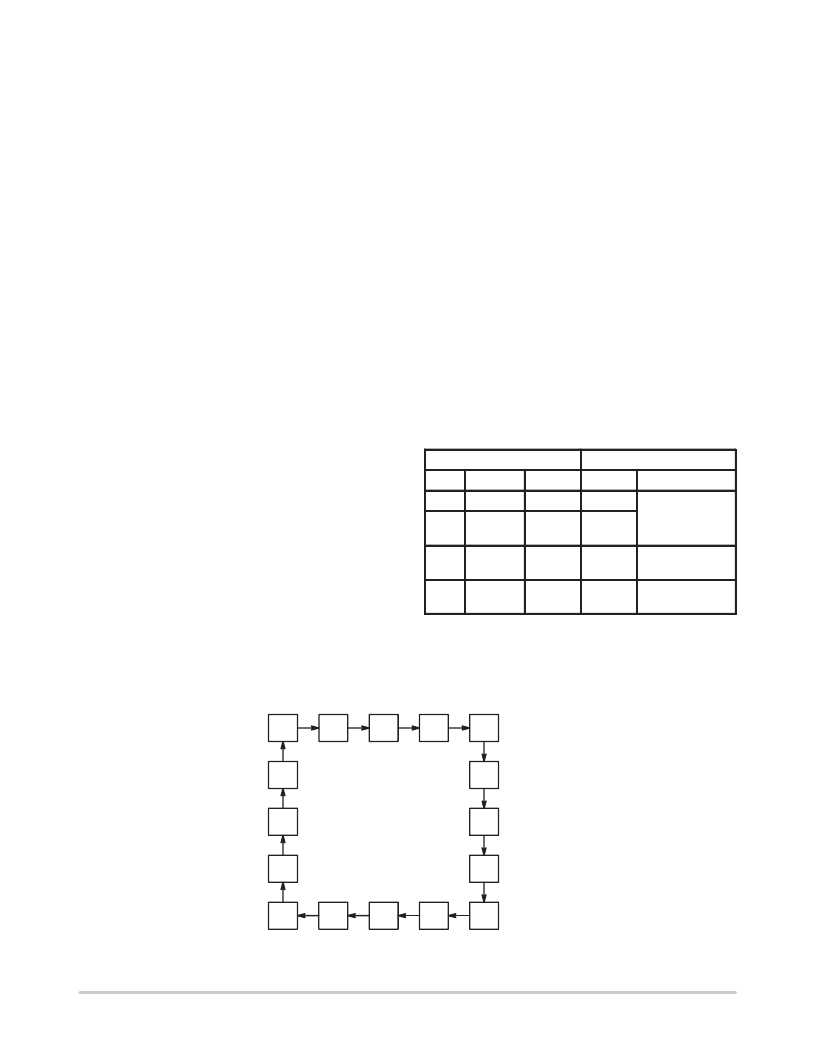

Table 1. Count Enable/Disable

Control Inputs

Result at Outputs

Load

Enable P

Enable T

Q0 – Q3

Ripple Carry Out

H

H

H

Count

High when Q0–Q3

are maximum*

L

H

H

No

Count

X

L

H

No

Count

High when Q0–Q3

are maximum*

X

X

L

No

Count

L

*Q0 through Q3 are maximum when Q3 Q2 Q1 Q0 = 1111.

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

OUTPUT STATE DIAGRAMS

Binary Counters

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC74HC161 | Presettable Counters |

| MC74HC161A | Presettable Counters |

| MC74HC16xAD | Presettable Counters |

| MC74HC16xAN | Presettable Counters |

| MC74HC161AD | PRESETTABLE COUNTERS HIGH-PERFORMANCE SILICON-GATE CMOS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC74HC173F | 制造商:Motorola Inc 功能描述: 制造商:ON Semiconductor 功能描述: |

| MC74HC173FEL | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC74HC173FL1 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC74HC173N | 制造商:ON Semiconductor 功能描述:Flip Flop D-Type Bus Interface Pos-Edge 3-ST 1-Element 16-Pin PDIP 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC74HC174AD | 功能描述:觸發(fā)器 2-6V CMOS Hex RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類型:CMOS 輸出類型: 傳播延遲時間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。