- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359664 > MC68HC11F1MFN (飛思卡爾半導(dǎo)體(中國)有限公司) ROM-based high-performance microcontrollers PDF資料下載

參數(shù)資料

| 型號(hào): | MC68HC11F1MFN |

| 廠商: | 飛思卡爾半導(dǎo)體(中國)有限公司 |

| 英文描述: | ROM-based high-performance microcontrollers |

| 中文描述: | 基于ROM的高性能微控制器 |

| 文件頁數(shù): | 48/124頁 |

| 文件大小: | 840K |

| 代理商: | MC68HC11F1MFN |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁當(dāng)前第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁

RESETS AND INTERRUPTS

5-4

TECHNICAL DATA

5.1.6 CONFIG Register

Bits [7:4] and 0 — Not implemented

Always read zero

NOCOP — COP System Disable

This bit is cleared out of reset in normal modes, enabling the COP system. It is set out

of reset in special modes. NOCOP is writable once in normal modes and at any time

in special modes.

0 = The COP system is enabled as the MCU comes out of reset.

1 = The COP system is disabled and does not generate system resets.

ROMON — Enable On-Chip ROM

Refer to

SECTION 4 OPERATING MODES AND ON-CHIP MEMORY

.

5.2 Effects of Reset

When a reset condition is recognized, the internal registers and control bits are forced

to an initial state. Depending on the cause of the reset and the operating mode, the

reset vector can be fetched from any of six possible locations. Refer to

Table 5-2

.

These initial states then control on-chip peripheral systems to force them to known

startup states, as follows:

5.2.1 CPU

After reset, the CPU fetches the restart vector from the appropriate address during the

first three cycles, and begins executing instructions. The stack pointer and other CPU

registers are indeterminate immediately after reset; however, the X and I interrupt

mask bits in the condition code register (CCR) are set to mask any interrupt requests.

Also, the S bit in the CCR is set to inhibit the STOP mode.

5.2.2 Memory Map

After reset, the INIT register is initialized to $00, putting the 192 bytes of RAM at loca-

tions $0040 through $00FF, and the control registers at locations $0000 through

$003F.

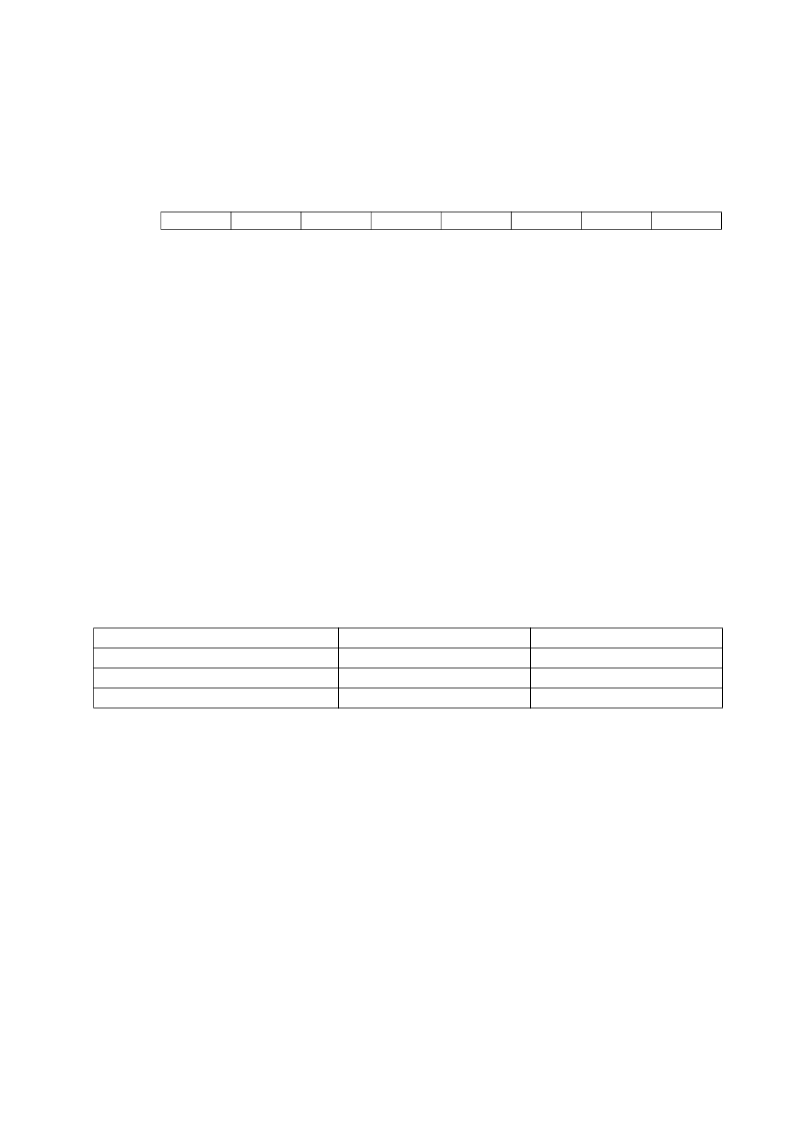

CONFIG

— Configuration Control Register

$003F

Bit 7

0

0

6

0

0

5

0

0

4

0

0

3

0

0

2

1

Bit 0

0

0

NOCOP

—

ROMON

—

RESET:

Table 5-2 Reset Cause, Reset Vector, and Operating Mode

Cause of Reset

Normal Mode Vector

$FFFE, FFFF

$FFFC, FFFD

$FFFA, FFFB

Special Test or Bootstrap

$BFFE, BFFF

$BFFC, $BFFD

$BFFA, BFFB

POR or RESET Pin

Clock Monitor Failure

COP Watchdog Time-out

F

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC68HC11F1MFN1 | ROM-based high-performance microcontrollers |

| MC68HC11F1MFU | ROM-based high-performance microcontrollers |

| MC68HC11F1MFU1 | ROM-based high-performance microcontrollers |

| MC68HC11F1MFU3 | ROM-based high-performance microcontrollers |

| MC68HC11F1MFU4 | ROM-based high-performance microcontrollers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC68HC11F1MFN1 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:ROM-based high-performance microcontrollers |

| MC68HC11F1MFN2 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Technical Summary 8-Bit Microcontroller |

| MC68HC11F1MFN3 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Technical Summary 8-Bit Microcontroller |

| MC68HC11F1MFN4 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Technical Summary 8-Bit Microcontroller |

| MC68HC11F1MFU | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:ROM-based high-performance microcontrollers |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。