- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359653 > MC68HC11F1FB3 (飛思卡爾半導(dǎo)體(中國)有限公司) ROM-based high-performance microcontrollers PDF資料下載

參數(shù)資料

| 型號: | MC68HC11F1FB3 |

| 廠商: | 飛思卡爾半導(dǎo)體(中國)有限公司 |

| 英文描述: | ROM-based high-performance microcontrollers |

| 中文描述: | 基于ROM的高性能微控制器 |

| 文件頁數(shù): | 113/124頁 |

| 文件大小: | 840K |

| 代理商: | MC68HC11F1FB3 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁當前第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁

ELECTRICAL CHARACTERISTICS

TECHNICAL DATA

A-9

NOTES:

1. Input clocks with duty cycles other than 50% affect bus performance. Timing parameters affected by input clock

duty cycle are identified by (a) and (b). To recalculate the approximate bus timing values, substitute the following

expressions in place of 1/8 t

cyc

in the above formulas, where applicable:

(a) (1-DC)

×

1/4 t

cyc

(b) DC

×

1/4 t

cyc

Where:

DC is the decimal value of duty cycle percentage (high time).

2. All timing is shown with respect to 20% V

DD

and 70% V

DD

, unless otherwise noted.

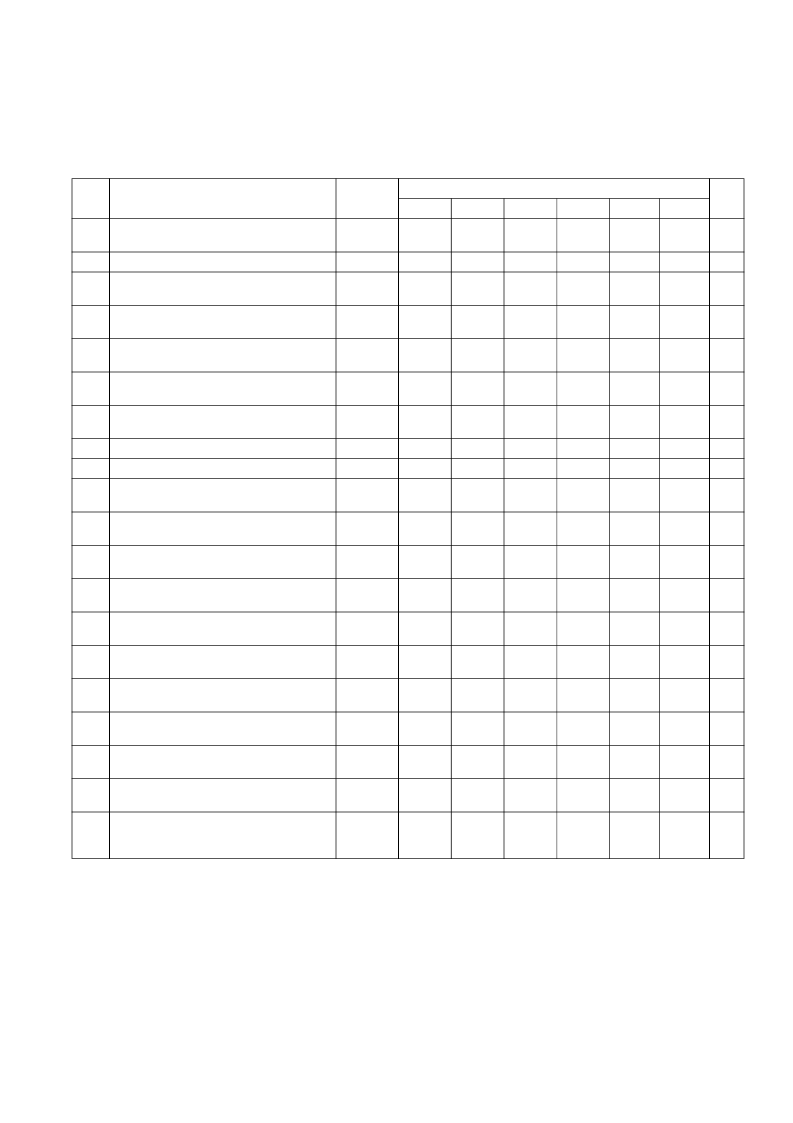

Table A-6 Expansion Bus Timing

Num

Characteristic

Symbol

1.0 MHz

Min

dc

2.0 MHz

Min

dc

3.0 MHz

Min

dc

Unit

Max

1.0

Max

2.0

Max

3.0

Frequency of Operation (E-Clock

Frequency)

Cycle Time

Pulse Width, E Low

PW

EL

= 1/2 t

cyc

-

23ns

Pulse Width, E High

PW

EH

= 1/2 t

cyc

-

28 ns

E and AS Rise Time

E and AS Fall Time

Address Hold Time

t

AH

= 1/8 t

cyc

-

29.5 ns

Non-Muxed Address Valid Time to E Rise

t

AV

= PW

EL

-

(t

ASD

+ 80 ns)

Read Data Setup Time

Read Data Hold Time (Max = t

MAD

)

Write Data Delay Time

t

DDW

= 1/8 t

cyc

+ 65.5 ns

Write Data Hold Time

t

DHW

= 1/8 t

cyc

-

30 ns

Muxed Address Valid Time to E Rise

t

AVM

= PW

EL -

(t

ASD

+ 90 ns) (Note 1a)

Muxed Address Valid Time to AS Fall

t

ASL

= PW

ASH

-

70 ns

Muxed Address Hold Time

t

AHL

= 1/8 t

cyc

-

30 ns

Delay Time, E to AS Rise

t

ASD

= 1/8 t

cyc

-

5 ns

Pulse Width, AS High

PW

ASH

= 1/4 t

cyc

-

30 ns

Delay Time, AS to E Rise

t

ASED

= 1/8 t

cyc

-

5 ns

MPU Address Access Time

t

ACCA

= t

cyc

– (PW

EL

– t

AVM

) – t

DSR

–t

f

MPU Access Time

t

ACCE

= PW

EH

-

t

DSR

Muxed Address Delay

(Previous Cycle MPU Read)

t

MAD

= t

ASD

+ 30 ns(Note 1a)

f

o

MHz

1

2

t

cyc

PW

EL

1000

477

—

—

500

227

—

—

333

146

—

—

ns

ns

3

PW

EH

472

—

222

—

141

—

ns

4A

4B

9

t

r

t

f

—

—

95.5

20

20

—

—

—

33

20

20

—

—

—

26

20

15

—

ns

ns

ns

(Note 1a)

t

AH

12

(Note 1a)

t

AV

281.5

—

94

—

54

—

ns

17

18

19

t

DSR

t

DHR

t

DDW

30

0

—

—

30

0

—

—

83

128

30

0

—

—

51

71

ns

ns

ns

145.5

190.5

(Note 1a)

21

(Note 1a)

t

DHW

95.5

—

33

—

26

—

ns

22

t

AVM

271.5

—

84

—

54

—

ns

24

t

ASL

151

—

26

—

13

—

ns

25

(Note 1b)

t

AHL

95.5

—

33

—

31

—

ns

26

(Note 1a)

t

ASD

115.5

—

53

—

31

—

ns

27

PW

ASH

221

—

96

—

63

—

ns

28

(Note 1b)

(Note 1a)

t

ASED

115.5

—

53

—

31

—

ns

29

t

ACCA

744.5

—

307

—

196

—

ns

35

t

ACCE

—

442

—

192

—

111

ns

36

t

MAD

145.5

—

83

—

51

—

ns

F

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC68HC11F1FB4 | ROM-based high-performance microcontrollers |

| MC68HC11F1VFU3 | ROM-based high-performance microcontrollers |

| MC68HC11F1VFU4 | ROM-based high-performance microcontrollers |

| MC68HC711A0CFB | ROM-based high-performance microcontrollers |

| MC68HC711A0CFB1 | ROM-based high-performance microcontrollers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC68HC11F1FB4 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:ROM-based high-performance microcontrollers |

| MC68HC11F1FN | 制造商:Motorola Inc 功能描述: |

| MC68HC11F1FN1 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:ROM-based high-performance microcontrollers |

| MC68HC11F1FN3 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:ROM-based high-performance microcontrollers |

| MC68HC11F1FN4 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:ROM-based high-performance microcontrollers |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。