- 您現(xiàn)在的位置:買賣IC網 > PDF目錄45226 > MC68HC11D3CFN3 (ABILIS SYSTEMS) 8-BIT, MROM, 3 MHz, MICROCONTROLLER, PQCC44 PDF資料下載

參數資料

| 型號: | MC68HC11D3CFN3 |

| 廠商: | ABILIS SYSTEMS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 3 MHz, MICROCONTROLLER, PQCC44 |

| 封裝: | PLASTIC, LCC-44 |

| 文件頁數: | 69/138頁 |

| 文件大小: | 1047K |

| 代理商: | MC68HC11D3CFN3 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁當前第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁

Central Processor Unit (CPU)

MC68HC711D3 Data Sheet, Rev. 2.1

36

Freescale Semiconductor

At the end of the interrupt service routine, a return-from interrupt (RTI) instruction is executed. The RTI

instruction causes the saved registers to be pulled off the stack in reverse order. Program execution

resumes at the return address.

Certain instructions push and pull the A and B accumulators and the X and Y index registers and are often

used to preserve program context. For example, pushing accumulator A onto the stack when entering a

subroutine that uses accumulator A and then pulling accumulator A off the stack just before leaving the

subroutine ensures that the contents of a register will be the same after returning from the subroutine as

it was before starting the subroutine.

3.2.5 Program Counter (PC)

The program counter, a 16-bit register, contains the address of the next instruction to be executed. After

reset, the program counter is initialized from one of six possible vectors, depending on operating mode

and the cause of reset.

See Table 3-1.

3.2.6 Condition Code Register (CCR)

This 8-bit register contains:

Five condition code indicators (C, V, Z, N, and H)

Two interrupt masking bits (IRQ and XIRQ)

One stop disable bit (S)

In the M68HC11 CPU, condition codes are updated automatically by most instructions. For example, load

accumulator A (LDAA) and store accumulator A (STAA) instructions automatically set or clear the N, Z,

and V condition code flags. Pushes, pulls, add B to X (ABX), add B to Y (ABY), and transfer/exchange

instructions do not affect the condition codes. Refer to Table 3-2, which shows what condition codes are

affected by a particular instruction.

3.2.6.1 Carry/Borrow (C)

The C bit is set if the arithmetic logic unit (ALU) performs a carry or borrow during an arithmetic operation.

The C bit also acts as an error flag for multiply and divide operations. Shift and rotate instructions operate

with and through the carry bit to facilitate multiple-word shift operations.

3.2.6.2 Overflow (V)

The overflow bit is set if an operation causes an arithmetic overflow. Otherwise, the V bit is cleared.

3.2.6.3 Zero (Z)

The Z bit is set if the result of an arithmetic, logic, or data manipulation operation is 0. Otherwise, the Z

bit is cleared. Compare instructions do an internal implied subtraction and the condition codes, including

Z, reflect the results of that subtraction. A few operations (INX, DEX, INY, and DEY) affect the Z bit and

no other condition flags. For these operations, only = and

≠ conditions can be determined.

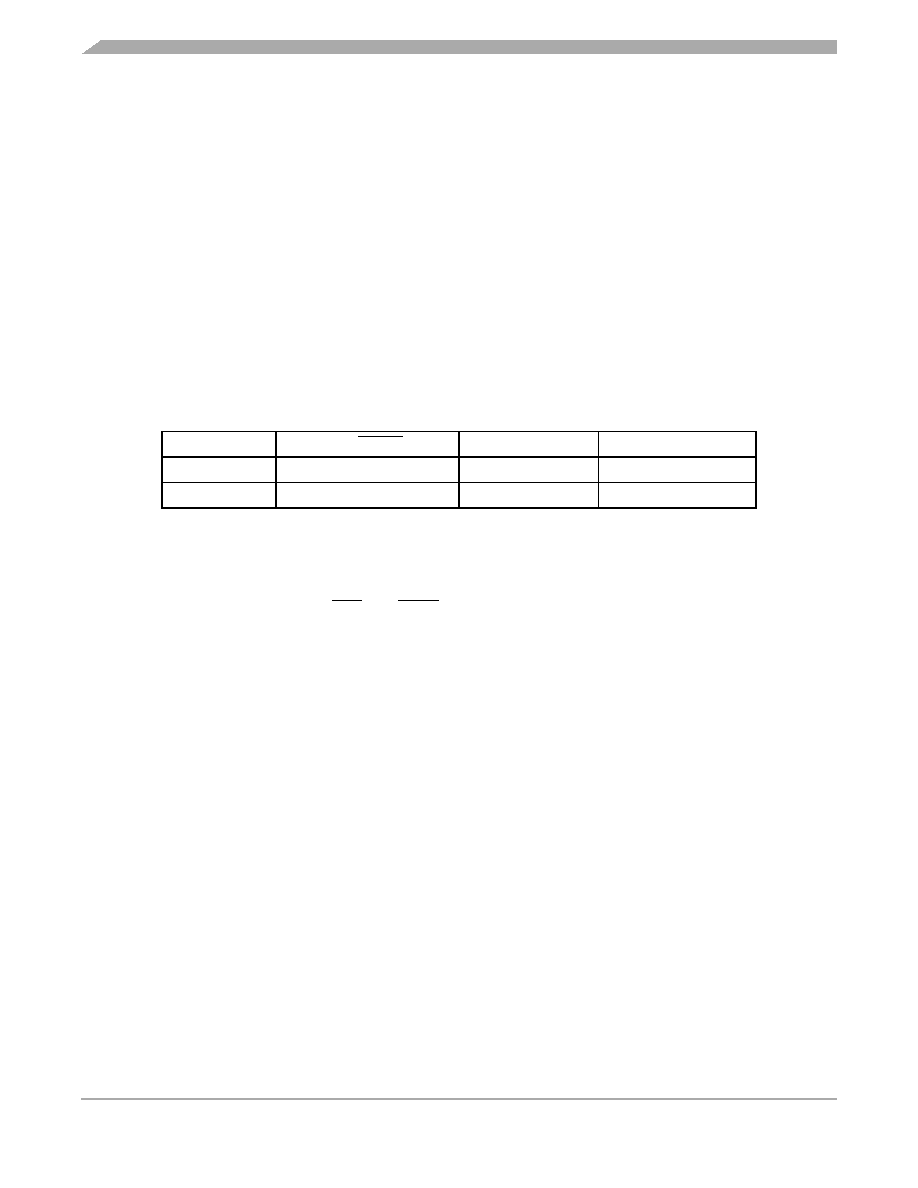

Table 3-1. Reset Vector Comparison

Mode

POR or RESET Pin

Clock Monitor

COP Watchdog

Normal

$FFFE, $FFFF

$FFFC, $FFFD

$FFFA, $FFFB

Test or boot

$BFFE, $BFFF

$BFFC, $FFFD

$BFFA, $FFFB

相關PDF資料 |

PDF描述 |

|---|---|

| MC68HC11D3CFB1 | 8-BIT, MROM, 3 MHz, MICROCONTROLLER, PQFP44 |

| MC68L11D0CFB3 | 8-BIT, MROM, 3 MHz, MICROCONTROLLER, PQFP44 |

| MC68HC11D0CFN2R2 | 8-BIT, MROM, 2 MHz, MICROCONTROLLER, PQCC44 |

| MC68HC11D3CP1 | 8-BIT, MROM, 3 MHz, MICROCONTROLLER, PDIP40 |

| MC68L11D0CFBE2R | 8-BIT, MROM, 2 MHz, MICROCONTROLLER, PQFP44 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| MC68HC11D3CFN4 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:ROM-based high-performance microcontrollers |

| MC68HC11D3CFU | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:ROM-based high-performance microcontrollers |

| MC68HC11D3CFU1 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:ROM-based high-performance microcontrollers |

| MC68HC11D3CFU3 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:ROM-based high-performance microcontrollers |

| MC68HC11D3CFU4 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:ROM-based high-performance microcontrollers |

發(fā)布緊急采購,3分鐘左右您將得到回復。