- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359731 > MC33742DWR2 (Motorola, Inc.) System Basis Chip (SBC) with Enhanced High-Speed CAN Transceiver PDF資料下載

參數(shù)資料

| 型號: | MC33742DWR2 |

| 廠商: | Motorola, Inc. |

| 元件分類: | CAN |

| 英文描述: | System Basis Chip (SBC) with Enhanced High-Speed CAN Transceiver |

| 中文描述: | 系統(tǒng)基礎(chǔ)芯片的增強型(SBC)的高速CAN收發(fā)器 |

| 文件頁數(shù): | 45/52頁 |

| 文件大小: | 1087K |

| 代理商: | MC33742DWR2 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁當(dāng)前第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

MOTOROLA ANALOG INTEGRATED CIRCUIT DEVICE DATA

33742

45

——————————————————

Interrupt Register (INTR)

Tables 35

through

37

contain various Interrupt Register

information. The INTR register allows masking or enabling the

interrupt source. A read operation identifies the interrupt

source.

Table 37

provides status bit information. The status

bits of the INTR register content are copies of the IOR, CAN,

TIM, and LPC registers status content. To clear the Interrupt

Register bits, the IOR, CAN, TIM, and/or LPC registers must be

cleared (read register) and the recovery condition must occur.

Errors bits are latched in the CAN register and the IOR register.

When the mask bit is set, the INT terminal goes low if the

appropriate condition occurs. Upon a wake-up condition from

Stop mode due to overcurrent detection (I

DDS-WU1

or I

DDS-WU2

),

an INT pulse is generated; however, INTR register content

remains at 0000 (not bit set into the INTR register).

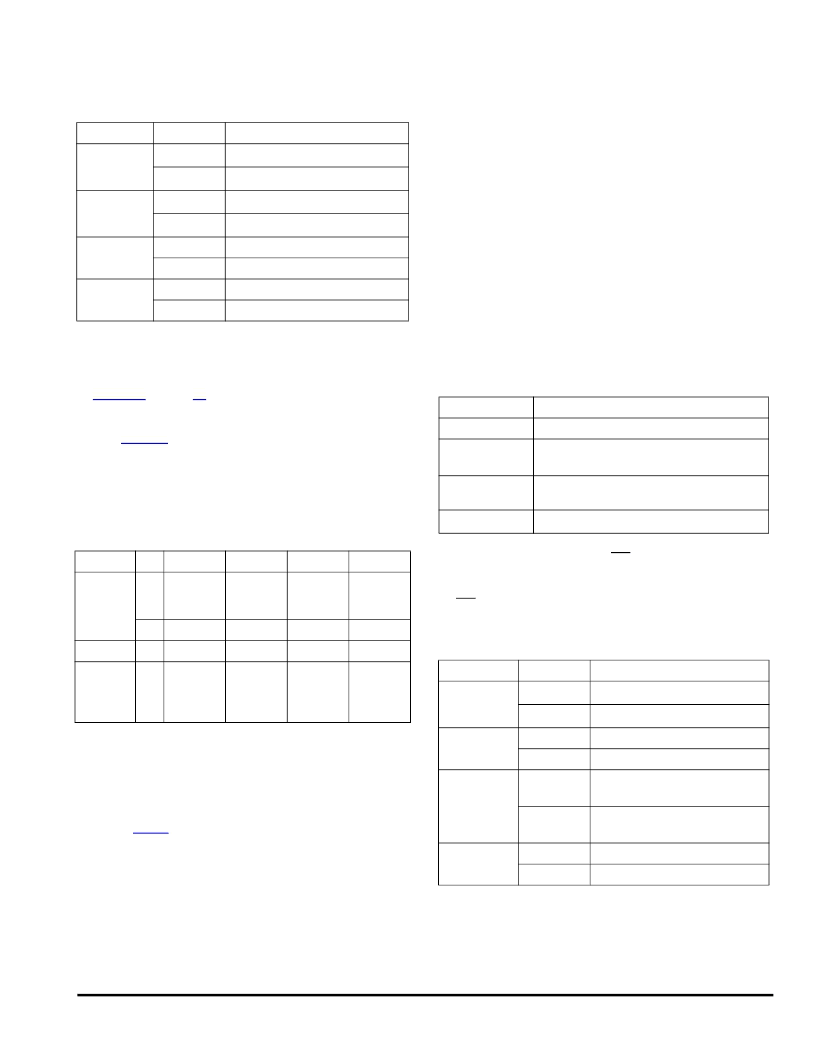

Table 34. LPC Status Bits

Name

Value

Failure Description

CANH2VDD

0

No CANH short to V

DD

.

1

CANH short to V

DD

.

CANH2BAT

0

No CANH short to V

SUP

.

1

CANH short to V

SUP

.

CANH2GND

0

No CANH short to GND.

1

CANH short to GND.

RXPR

0

No RXD permanent recessive.

1

RXD permanent recessive.

Table 35. Interrupt Register

INTR

R/W

D3

D2

D1

D0

$111b

W

VSUPLOW

HSOT-

V2LOW

(Note 64)

VDDTEMP

CANF

R

VSUPLOW

HSOT

VDDTEMP

CANF

Reset Value

–

0

0

0

0

Reset

Condition

(Write)

(Note 65)

–

POR, RST

POR, RST

POR, RST

POR, RST

Notes

64.

If only HSOT-V2LOW interrupt is selected (only bit D2 set in

INTR register), reading INTR register bit D2 leads to two

possibilities:

1. Bit D2 = 1: Interrupt source is HSOT.

2. Bit D2 = 0: Interrupt source is V2LOW.

HSOT and V2LOW bits status are available in the IOR register.

See

Table 8

, page 38, for definitions of reset conditions.

65.

Table 36. Interrupt Register Control Bits

Name

Description

CANF

Mask bit for CAN failures.

VDDTEMP

Mask bit for V

DD

medium temperature

(pre-warning).

HSOT-V2LOW

Mask bit for HS overtemperature AND

V2 < 4.0 V.

VSUPLOW

Mask bit for V

SUP

< 6.1 V.

Table 37. Interrupt Register Status Bits

Name

Value

Description

VSUPLOW

0

No V

SUP

< 6.1 V.

1

V

SUP

< 6.1 V.

HSOT

0

No HS overtemperature.

1

HS overtemperature.

VDDTEMP

0

No V

DD

medium temperature (pre-

warning).

1

V

DD

medium temperature (pre-

warning).

CANF

0

No CAN failure.

1

CAN failure.

F

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC68HC11A1 | 8-Bit Microcontrollers |

| MC68HC11A1CFN3 | HCMOS Single-Chip Microcontroller |

| MC68HC11A1CFU2 | HCMOS Single-Chip Microcontroller |

| MC68HC11A1CFU3 | HCMOS Single-Chip Microcontroller |

| MC68HC11A1CP2 | HCMOS Single-Chip Microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC33742EP | 功能描述:CAN 接口集成電路 SBC_ECAN_HS RoHS:否 制造商:Texas Instruments 類型:Transceivers 工作電源電壓:5 V 電源電流: 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:SOIC-8 封裝:Tube |

| MC33742EPR2 | 功能描述:CAN 接口集成電路 SBC_ECAN_HS RoHS:否 制造商:Texas Instruments 類型:Transceivers 工作電源電壓:5 V 電源電流: 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:SOIC-8 封裝:Tube |

| MC33742PEG | 功能描述:CAN 接口集成電路 SBC-E-HS-CAN RoHS:否 制造商:Texas Instruments 類型:Transceivers 工作電源電壓:5 V 電源電流: 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:SOIC-8 封裝:Tube |

| MC33742PEGR2 | 功能描述:CAN 接口集成電路 SBC-E-HS-CAN RoHS:否 制造商:Texas Instruments 類型:Transceivers 工作電源電壓:5 V 電源電流: 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:SOIC-8 封裝:Tube |

| MC33742PEP | 功能描述:CAN 接口集成電路 SBC-E-HS-CAN RoHS:否 制造商:Texas Instruments 類型:Transceivers 工作電源電壓:5 V 電源電流: 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:SOIC-8 封裝:Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。