- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382298 > MC14521BD (ON SEMICONDUCTOR) 24-Stage Frequency Divider PDF資料下載

參數(shù)資料

| 型號: | MC14521BD |

| 廠商: | ON SEMICONDUCTOR |

| 元件分類: | 諧振器 |

| 英文描述: | 24-Stage Frequency Divider |

| 中文描述: | 4000/14000/40000 SERIES, PRESCALER, PDSO16 |

| 封裝: | SOIC-16 |

| 文件頁數(shù): | 1/12頁 |

| 文件大?。?/td> | 219K |

| 代理商: | MC14521BD |

Semiconductor Components Industries, LLC, 2000

March, 2000 – Rev. 3

1

Publication Order Number:

MC14521B/D

The MC14521B consists of a chain of 24 flip–flops with an input

circuit that allows three modes of operation. The input will function as

a crystal oscillator, an RC oscillator, or as an input buffer for an

external oscillator. Each flip–flop divides the frequency of the

previous flip–flop by two, consequently this part will count up to 2

24

=

16,777,216. The count advances on the negative going edge of the

clock. The outputs of the last seven–stages are available for added

flexibility.

All Stages are Resettable

Reset Disables the RC Oscillator for Low Standby Power Drain

RC and Crystal Oscillator Outputs Are Capable of Driving External

Loads

Test Mode to Reduce Test Time

V

DD

′

and V

SS

′

Pins Brought Out on Crystal Oscillator Inverter to

Allow the Connection of External Resistors for Low–Power

Operation

Supply Voltage Range = 3.0 Vdc to 18 Vdc

Capable of Driving Two Low–power TTL Loads or One Low–power

Schottky TTL Load over the Rated Temperature Range.

MAXIMUM RATINGS

(Voltages Referenced to V

SS

) (Note 2.)

Symbol

Parameter

Value

Unit

V

DD

DC Supply Voltage Range

–0.5 to +18.0

V

V

in

, V

out

Input or Output Voltage Range

(DC or Transient)

–0.5 to V

DD

+ 0.5

V

I

in

, I

out

Input or Output Current

(DC or Transient) per Pin

±

10

mA

P

D

Power Dissipation,

per Package (Note 3.)

500

mW

T

A

Ambient Temperature Range

–55 to +125

°

C

T

stg

Storage Temperature Range

–65 to +150

°

C

T

L

Lead Temperature

(8–Second Soldering)

260

°

C

2. Maximum Ratings are those values beyond which damage to the device

may occur.

3. Temperature Derating:

Plastic “P and D/DW” Packages: – 7.0 mW/ C From 65 C To 125 C

This device contains protection circuitry to guard against damage due to high

static voltages or electric fields. However, precautions must be taken to avoid

applications of any voltage higher than maximum rated voltages to this

high–impedance circuit. For proper operation, V

in

and V

out

should be constrained

to the range V

SS

(V

in

or V

out

)

V

DD

.

Unused inputs must always be tied to an appropriate logic voltage level (e.g.,

either V

SS

or V

DD

). Unused outputs must be left open.

http://onsemi.com

A

WL or L

YY or Y

WW or W = Work Week

= Assembly Location

= Wafer Lot

= Year

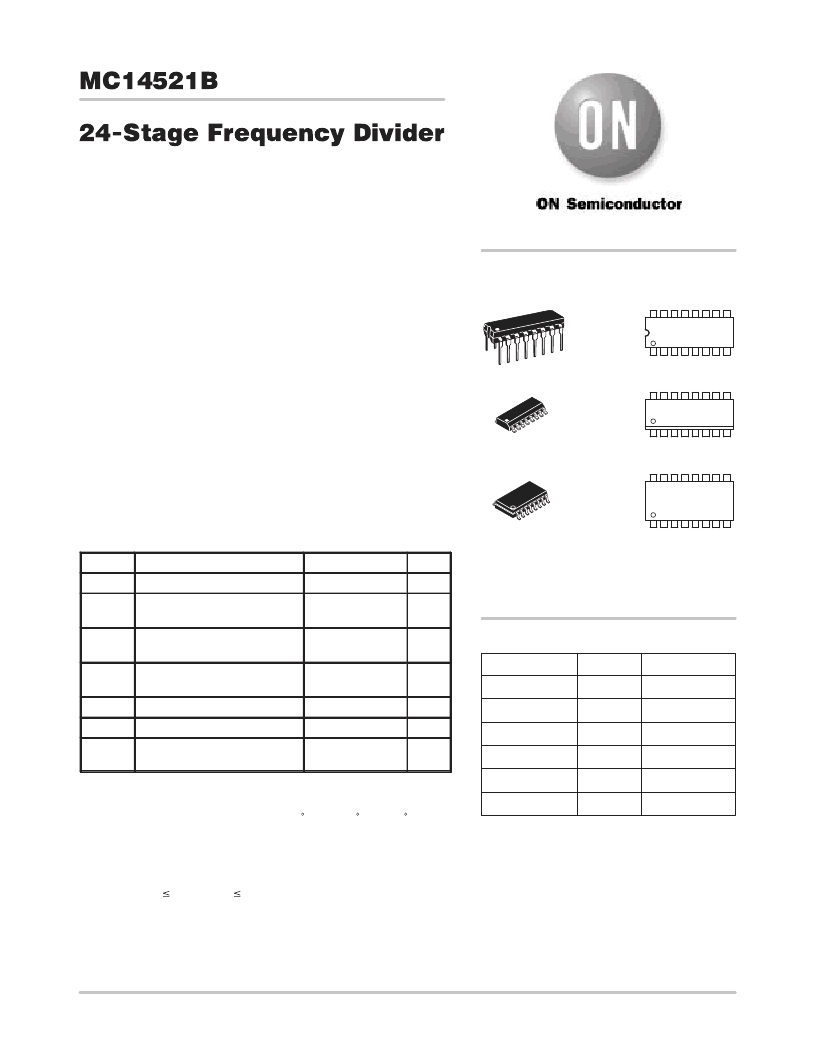

Device

Package

Shipping

ORDERING INFORMATION

MC14521BCP

PDIP–16

2000/Box

MC14521BD

SOIC–16

48/Rail

MC14521BDR2

SOIC–16

2500/Tape & Reel

1. For ordering information on the EIAJ version of

the SOIC packages, please contact your local

ON Semiconductor representative.

MARKING

DIAGRAMS

16

1

PDIP–16

P SUFFIX

CASE 648

MC14521BCP

AWLYYWW

SOIC–16

D SUFFIX

CASE 751B

1

16

14521B

AWLYWW

SOEIAJ–16

F SUFFIX

CASE 966

1

16

MC14521B

AWLYWW

MC14521BFEL

SOEIAJ–16

See Note 1.

MC14521BFR2

SOEIAJ–16

See Note 1.

MC14521BF

SOEIAJ–16

See Note 1.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC14521BDR2 | 24-Stage Frequency Divider |

| MC14521BF | 24-Stage Frequency Divider |

| MC14521BFEL | Automotive Catalog Single-Channel High-Speed Mosfet Driver 5-SOT-23 -40 to 125 |

| MC14521BFR2 | Non-inverting Fast Synchronous Buck MOSFET Drivers with Enable 14-SOIC |

| MC14526BDWR2 | Presettable 4-Bit Down Counters |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC14521BDG | 功能描述:增效器/分頻器 LOG CMOS OSILATR 24STAGE RoHS:否 制造商:Texas Instruments 產(chǎn)品:Multiplier 邏輯系列: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:Through Hole 封裝 / 箱體:PDIP-14 |

| MC14521BDR2 | 功能描述:增效器/分頻器 LOG CMOS OSILATR 24STAGE RoHS:否 制造商:Texas Instruments 產(chǎn)品:Multiplier 邏輯系列: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:Through Hole 封裝 / 箱體:PDIP-14 |

| MC14521BDR2G | 功能描述:增效器/分頻器 LOG CMOS OSILATR 24STAGE RoHS:否 制造商:Texas Instruments 產(chǎn)品:Multiplier 邏輯系列: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:Through Hole 封裝 / 箱體:PDIP-14 |

| MC14521BDR2G-CUT TAPE | 制造商:ON 功能描述:MC14521B Series 3 to 18 Vdc 24-Stage Frequency Divider - SOIC-16 |

| MC14521BF | 制造商:ON Semiconductor 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。