- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45193 > MB90W224AZF (FUJITSU LTD) 16-BIT, UVPROM, 16 MHz, MICROCONTROLLER, CQFP120 PDF資料下載

參數(shù)資料

| 型號: | MB90W224AZF |

| 廠商: | FUJITSU LTD |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 16-BIT, UVPROM, 16 MHz, MICROCONTROLLER, CQFP120 |

| 封裝: | CERAMIC, QFP-120 |

| 文件頁數(shù): | 24/105頁 |

| 文件大小: | 1800K |

| 代理商: | MB90W224AZF |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁

25

MB90220 Series

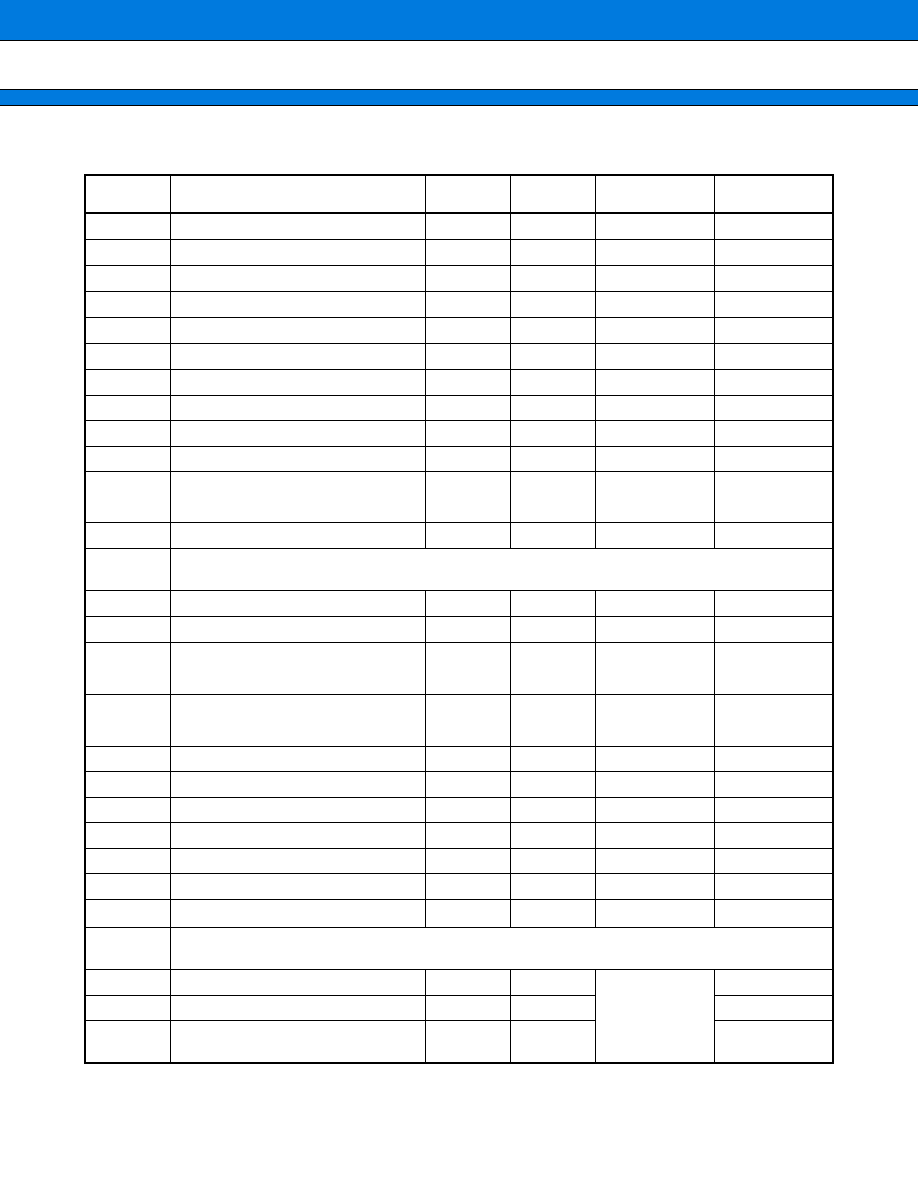

s I/O MAP

(Continued)

Address

Register

name

Access

Resouce

name

Initial value

000000H*3

Port 0 data register

PDR0

R/W

Port 0

X XXXXXXX

000001H*3

Port 1 data register

PDR1

R/W

Port 1

X XXXXXXX

000002H*3

Port 2 data register

PDR2

R/W

Port 2

X XXXXXXX

000003H*3

Port 3 data register

PDR3

R/W

Port 3

X XXXXXXX

000004H*3

Port 4 data register

PDR4

R/W

Port 4

X XXXXXXX

000005H*3

Port 5 data register

PDR5

R/W

Port 5

X XXXXXXX

000006H

Port 6 data register

PDR6

R/W

Port 6

1 1111111

000007H

Port 7 data register

PDR7

R

Port 7

X XXXXXXX

000008H

Port 8 data register

PDR8

R/W

Port 8

X XXXXXXX

000009H

Port 9 data register

PDR9

R/W

Port 9

1 1111111

00000AH

Port A data register

PDRA

R/W

Port A

X XXXXXXX

00000BH

Port B data register

PDRB

R/W

Port B

X XXXXXXX

00000CH

Port C data register

PDRC

R/W

Port C

– – XXXXXX

00000DH

to 0FH

(Reserved area)*1

000010H*3

Port 0 data direction register

DDR0

R/W

Port 0

0 0000000

000011H*3

Port 1 data direction register

DDR1

R/W

Port 1

0 0000000

000012H*3

Port 2 data direction register

DDR2

R/W

Port 2

0 0000000

000013H*3

Port 3 data direction register

DDR3

R/W

Port 3

0 0000000

000014H*3

Port 4 data direction register

DDR4

R/W

Port 4

0 0000000

000015H*3

Port 5 data direction register

DDR5

R/W

Port 5

0 0000000

000016H

Port 6 analog input enable register

ADER0

R/W

Port 6

1 1111111

000017H

Port 7 data direction register

DDR7

R/W

Port 7

1 1111111

000018H

Port 8 data direction register

DDR8

R/W

Port 8

0 0000000

000019H

Port 9 analog input enable register

ADER1

R/W

Port 9

1 1111111

00001AH

Port A data direction register

DDRA

R/W

Port A

0 0000000

00001BH

Port B data direction register

DDRB

R/W

Port B

0 0000000

00001CH

Port C data direction register

DDRC

R/W

Port C

–– 000000

00001DH

to 1FH

(Reserved area)*1

000020H

Mode control register 0

UMC0

R/W

UART 0 (ch.0)

0 0000100

000021H

Status register 0

USR0

R/W

0 0010000

000022H

Input data register 0

/output data register 0

UIDR0

/UODR0

R/W

X XXXXXXX

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB90W224AZF | 16-BIT, UVPROM, 16 MHz, MICROCONTROLLER, CQFP120 |

| MB91101APF-G-JNE1 | 32-BIT, 50 MHz, RISC MICROCONTROLLER, PQFP100 |

| MB91106PFV-XXX | 32-BIT, MROM, 50 MHz, RISC MICROCONTROLLER, PQFP100 |

| MB91107APMC1 | RISC MICROCONTROLLER, PQFP120 |

| MB91107APFV | RISC MICROCONTROLLER, PQFP120 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MB-910 | 制造商:Circuit Test 功能描述:BREADBOARD WIRING KIT - 350 PCS |

| MB9100100 | 制造商:COM/DUO 功能描述:FAN 4-6WKS |

| MB9100-100 | 制造商:COM/DUO 功能描述:FAN 4-6WKS |

| MB91101 | 制造商:Panasonic Industrial Company 功能描述:IC |

| MB91101A | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:32-bit RISC Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。