- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄11678 > MAX9257GCM+ (Maxim Integrated Products)IC SER/DESER PROG 48-LQFP PDF資料下載

參數(shù)資料

| 型號(hào): | MAX9257GCM+ |

| 廠商: | Maxim Integrated Products |

| 文件頁(yè)數(shù): | 18/52頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC SER/DESER PROG 48-LQFP |

| 其它有關(guān)文件: | Automotive Product Guide |

| 產(chǎn)品培訓(xùn)模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標(biāo)準(zhǔn)包裝: | 250 |

| 功能: | 串行器/解串器 |

| 數(shù)據(jù)速率: | 840Mbps |

| 輸入類型: | 串行 |

| 輸出類型: | LVDS |

| 輸入數(shù): | 16 |

| 輸出數(shù): | 1 |

| 電源電壓: | 3 V ~ 3.6 V |

| 工作溫度: | -40°C ~ 105°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 48-LQFP |

| 供應(yīng)商設(shè)備封裝: | 48-LQFP(7x7) |

| 包裝: | 管件 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)當(dāng)前第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)

tracks and passes the spread to the data and clock out-

puts. The PRATE range of 00 and 01 (5MHz ≤ PCLK ≤

20MHz) supports all the spread options. The PRATE

range of 10 and 11 (20MHz ≤ PCLK ≤ 70MHz) requires

that the spread be 2% or less.

Pixel Clock Jitter Filter

The MAX9257 has a PLL to filter high-frequency pixel

clock jitter on PCLK_IN. The FPLL can be bypassed by

writing 1 to REG4[2]. The FPLL improves the

MAX9258’s data recovery by filtering out the high-fre-

quency components from the pixel clock that the

MAX9258 cannot track. The 3dB bandwidth of the FPLL

is 100kHz (typ).

LVDS Output Preemphasis (SDO±)

The MAX9257 features programmable preemphasis

where extra current is added when the LVDS outputs

transition on the serial link. Preemphasis provides addi-

tional current to the normal drive current. For example,

20% preemphasis provides 20% greater current than

the normal drive current. Current is boosted only on the

transitions and returns to the normal drive current after

switching. Select the preemphasis level to optimize the

eye diagram. Preemphasis boosts the high-frequency

content of the LVDS outputs to enable driving greater

cable lengths. The amount of preemphasis is pro-

grammed in REG12[7:5] (Table 21).

VSYNC, HSYNC, and Pixel Clock Polarity

PCLK: The MAX9257 is programmable to latch data on

either rising or falling edge of PCLK. The polarity of

PCLKOUT at the MAX9258 can be independent of the

MAX9257 PCLK active edge. The polarity of PCLK can

be programmed using REG4[5] of the MAX9257 and

the MAX9258.

VSYNC: The MAX9257 and the MAX9258 enter control

channel on the falling edge of VSYNC. The default reg-

ister settings are VSYNC active falling edge for both the

MAX9257 and the MAX9258. If the VSYNC active edge

is programmed for rising edge at the MAX9257, the

MAX9258 VSYNC active edge must also be pro-

grammed for rising edge to reproduce VSYNC rising

edge at the MAX9258 output. However, matching the

polarity of the VSYNC active edge between the

MAX9257 and the MAX9258 is not a requirement for

proper operation.

HSYNC: HSYNC active-edge polarity is programmable

for the MAX9258.

General Purpose I/Os (GPIOs)

The MAX9257 has up to 10 GPIOs available. GPIO8

and GPIO9 are always available while GPIO[0:7] are

available depending on the parallel-word width (Table

22). If GPIOs are not available, the corresponding GPIO

bits are not used.

MAX9257/MAX9258

______________________________________________________________________________________

25

Fully Programmable Serializer/Deserializer

with UART/I2C Control Channel

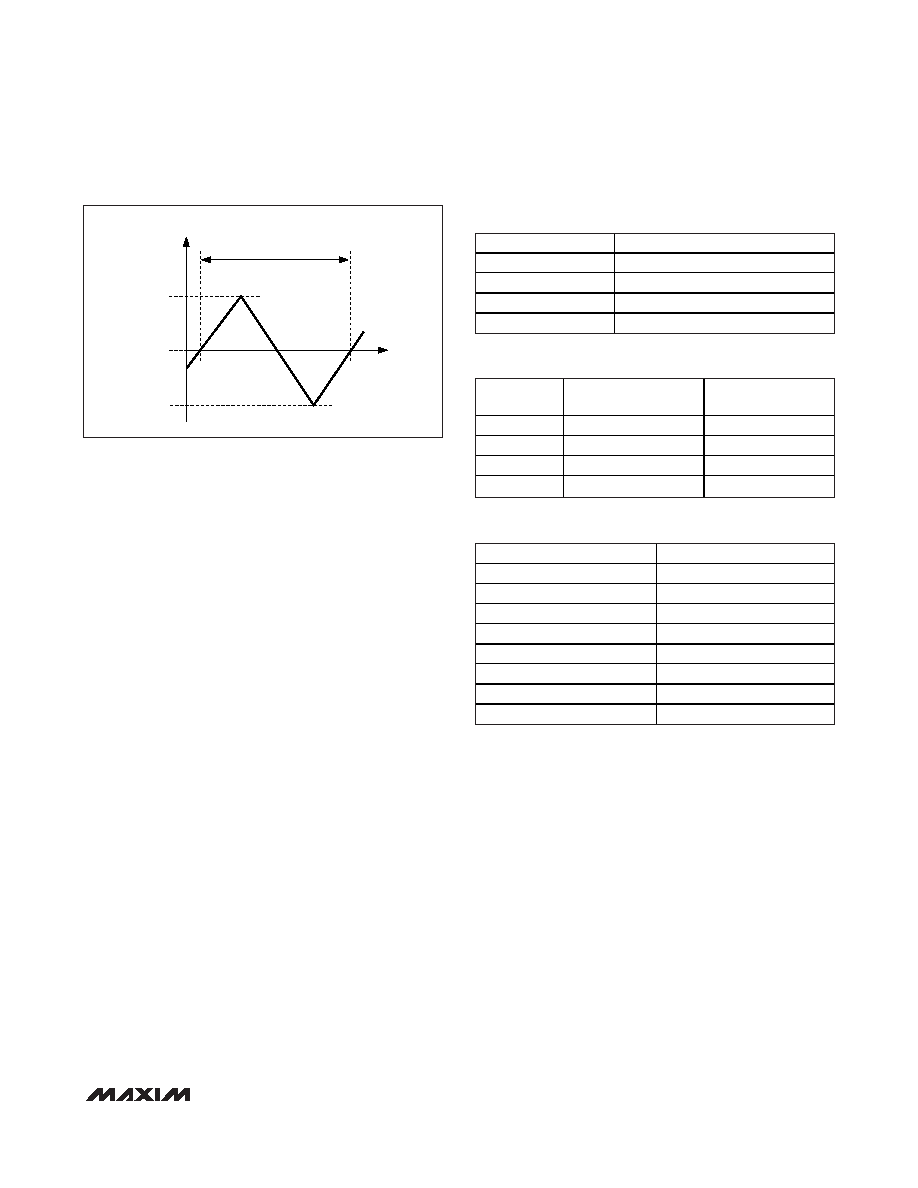

FREQUENCY

TIME

fSPREAD (MAX)

fPCLK_IN

fSPREAD (MIN)

1/fSSM

Figure 21. Simplified Modulation Profile for the MAX9257/MAX9258

PRATE (REG1[7:6])

SPREAD (%)

00

Off

01

±2

10

Off

11

±4

Table 17. MAX9258 Spread

PRATE

(REG1[7:6])

MODULATION RATE

fSSM RANGE (kHz)

00

PCLK/312

16 to 32

01

PCLK/520

19.2 to 38.5

10

PCLK/1040

19.2 to 38.5

11

PCLK/1248

32 to 56

Table 18. MAX9258 Modulation Rate

REG1[7:5]

SPREAD (%)

000

Off

001

±1.5

010

±1.75

011

±2

100

Off

101

±3

110

±3.5

111

±4

Table 19. MAX9257 LVDS Output Spread

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| R5F562N7BDFB#V0 | MCU 32BIT FLASH 384KROM 144LQFP |

| MAX9257GTL+ | IC SER/DESER PROG 40-TQFN |

| R5F562N7BDLE#U0 | MCU 32BIT FLASH 384KROM 145TFLGA |

| R5F562N7ADBG#U0 | MCU 32BIT FLASH 384KROM 176LFBGA |

| MAX9214EUM+T | IC DESERIALIZER PROG 48TSSOP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX9257GCM/V+ | 功能描述:串行器/解串器 - Serdes Prog Serializer / Deserializer RoHS:否 制造商:Texas Instruments 類型:Deserializer 數(shù)據(jù)速率:1.485 Gbit/s 輸入類型:ECL/LVDS 輸出類型:LVCMOS 輸入端數(shù)量:1 輸出端數(shù)量:20 工作電源電壓:2.375 V to 2.625 V 工作溫度范圍:0 C to + 70 C 封裝 / 箱體:TQFP-64 |

| MAX9257GCM/V+T | 功能描述:串行器/解串器 - Serdes Prog Serializer / Deserializer RoHS:否 制造商:Texas Instruments 類型:Deserializer 數(shù)據(jù)速率:1.485 Gbit/s 輸入類型:ECL/LVDS 輸出類型:LVCMOS 輸入端數(shù)量:1 輸出端數(shù)量:20 工作電源電壓:2.375 V to 2.625 V 工作溫度范圍:0 C to + 70 C 封裝 / 箱體:TQFP-64 |

| MAX9257GCM+ | 功能描述:串行器/解串器 - Serdes Prog Serializer / Deserializer RoHS:否 制造商:Texas Instruments 類型:Deserializer 數(shù)據(jù)速率:1.485 Gbit/s 輸入類型:ECL/LVDS 輸出類型:LVCMOS 輸入端數(shù)量:1 輸出端數(shù)量:20 工作電源電壓:2.375 V to 2.625 V 工作溫度范圍:0 C to + 70 C 封裝 / 箱體:TQFP-64 |

| MAX9257GCM+T | 功能描述:串行器/解串器 - Serdes Prog Serializer / Deserializer RoHS:否 制造商:Texas Instruments 類型:Deserializer 數(shù)據(jù)速率:1.485 Gbit/s 輸入類型:ECL/LVDS 輸出類型:LVCMOS 輸入端數(shù)量:1 輸出端數(shù)量:20 工作電源電壓:2.375 V to 2.625 V 工作溫度范圍:0 C to + 70 C 封裝 / 箱體:TQFP-64 |

| MAX9257GTL/V+ | 功能描述:串行器/解串器 - Serdes Prog Serializer / Deserializer RoHS:否 制造商:Texas Instruments 類型:Deserializer 數(shù)據(jù)速率:1.485 Gbit/s 輸入類型:ECL/LVDS 輸出類型:LVCMOS 輸入端數(shù)量:1 輸出端數(shù)量:20 工作電源電壓:2.375 V to 2.625 V 工作溫度范圍:0 C to + 70 C 封裝 / 箱體:TQFP-64 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。