M

Quad Bus LVDS Transceiver

______________________________________________________________________________________

11

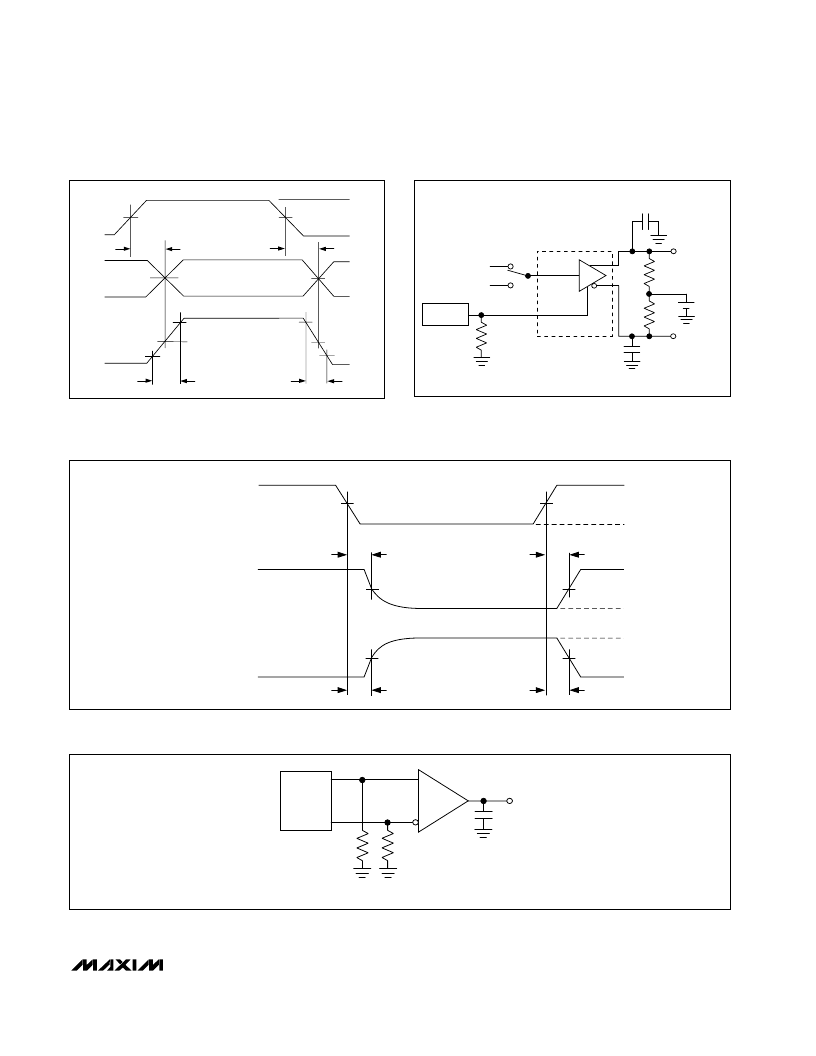

0

V

OH

V

OL

DIN_

RIN_-

RIN_+

V

OD

V

CC

t

PHLD

50%

0

t

THL

20%

0

80%

80%

0

t

TLH

20%

0 DIFFERENTIAL

t

PLHD

50%

V

OD

= (V

DO_+/RIN_+

- V

DO_-/RIN_-

)

Figure 4. Driver Propagation Delay and Transition Time

Waveforms

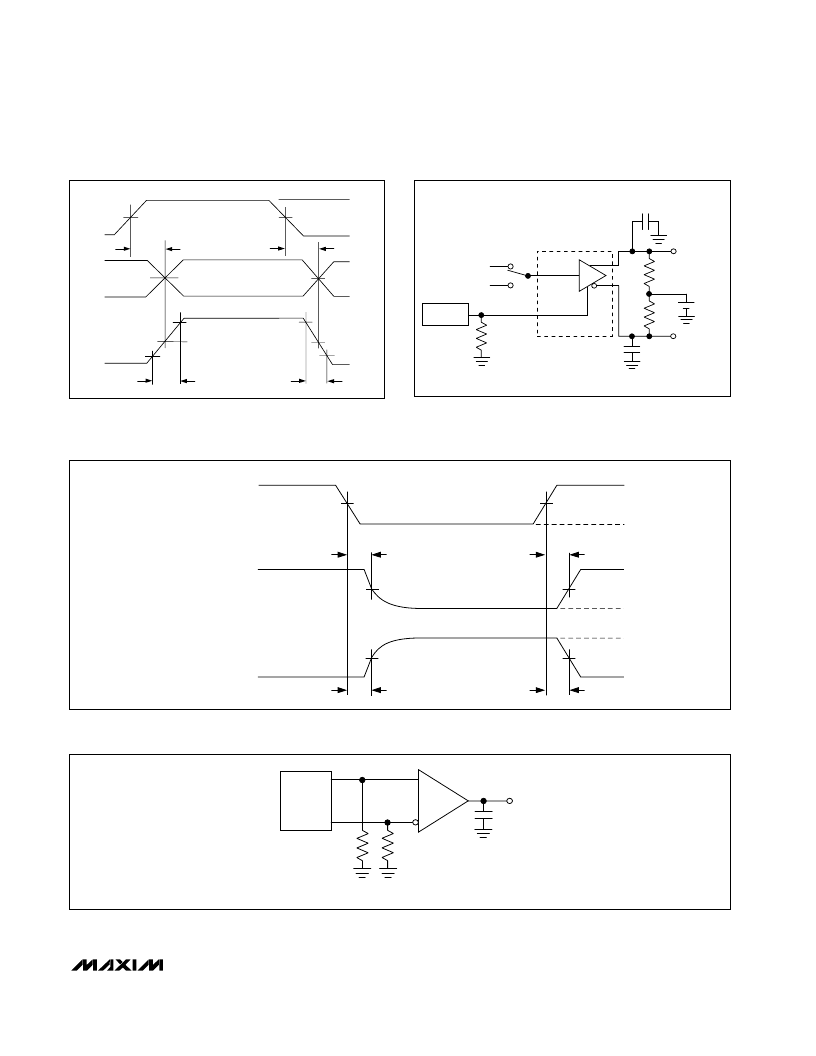

GND

DIN_

DO_-/RIN_-

DO_+/RIN_+

1/4 MAX9157

GENERATOR

+1.2V

50

C

L

R

L

/2

R

L

/2

V

CC

C

L

DE_

Figure 5. Driver High-Impedance Delay Test Circuit

50%

DE_

DO_+/RIN_+ WHEN DIN_ = 0

DO_-/RIN_- WHEN DIN_ = V

CC

D0_+/RIN_+ WHEN DIN_ = V

CC

DO_-/RIN_- WHEN DIN_ = 0

50%

t

PLZ

t

PHZ

t

PZL

t

PZH

V

CC

0

1.2V

V

OL

V

OH

1.2V

50%

50%

50%

50%

Figure 6. Driver High-Impedance Delay Waveform

DO_+/RIN_+

DO_-/RIN_-

RO_

RECEIVER ENABLED

1/4 MAX9157

*50

REQUIRED FOR PULSE GENERATOR TERMINATION.

PULSE

GENERATOR

50

*

50

*

C

L

Figure 7. Receiver Transition Time and Propagation Delay Test Circuit