- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄10505 > MAX9125ESE+ (Maxim Integrated Products)IC QUAD LVDS LINE RCVR 16-SOIC PDF資料下載

參數(shù)資料

| 型號: | MAX9125ESE+ |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 9/12頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC QUAD LVDS LINE RCVR 16-SOIC |

| 產(chǎn)品培訓(xùn)模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標(biāo)準(zhǔn)包裝: | 50 |

| 類型: | 接收器 |

| 驅(qū)動器/接收器數(shù): | 0/4 |

| 規(guī)程: | LVDS |

| 電源電壓: | 3 V ~ 3.6 V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 16-SOIC(0.154",3.90mm 寬) |

| 供應(yīng)商設(shè)備封裝: | 16-SOIC |

| 包裝: | 管件 |

| 產(chǎn)品目錄頁面: | 1408 (CN2011-ZH PDF) |

MAX9125/MAX9126

Detailed Description

The LVDS interface standard is a signaling method

intended for point-to-point communication over a con-

trolled-impedance medium as defined by the ANSI

TIA/EIA-644 and IEEE 1596.3 standards. The LVDS

standard uses a lower voltage swing than other com-

mon communication standards, achieving higher data

rates with reduced power consumption while reducing

EMI emissions and system susceptibility to noise.

The MAX9125/MAX9126 are 500Mbps, four-channel

LVDS receivers intended for high-speed, point-to-point,

low-power applications. Each channel accepts an

LVDS input and translates it to an LVTTL/LVCMOS out-

put. The receiver is capable of detecting differential

signals as low as 100mV and as high as 1V within an

input voltage range of 0 to 2.4V. The 250mV to 400mV

differential output of an LVDS driver is nominally cen-

tered around a +1.2V offset. This offset, coupled with

the receiver’s 0 to 2.4V input voltage range, allows an

approximate ±1V shift in the signal (as seen by the

receiver). This allows for a difference in ground refer-

ences of the transmitter and the receiver, the common-

mode effects of coupled noise, or both. The LVDS

standards specify an input voltage range of 0 to 2.4V

referenced to receiver ground.

The MAX9126 has an integrated termination resistor

internally connected across each receiver input. The

internal termination saves board space, eases layout,

and reduces “stub length” compared to an external ter-

mination resistor. In other words, the transmission line

is terminated on the IC.

Quad LVDS Line Receivers with

Integrated Termination

6

_______________________________________________________________________________________

ENABLES

INPUTS

OUTPUT

EN

EN

(IN_+) - (IN_-)

OUT_

LH

X

Z

VID

≥ +100mV

H

VID

≤ -100mV

L

MAX9125

Open, undriven short, or

undriven 100

parallel

termination

All other combinations of ENABLE inputs

MAX9126

Open or undriven short

H

Table 1. Input/Output Function Table

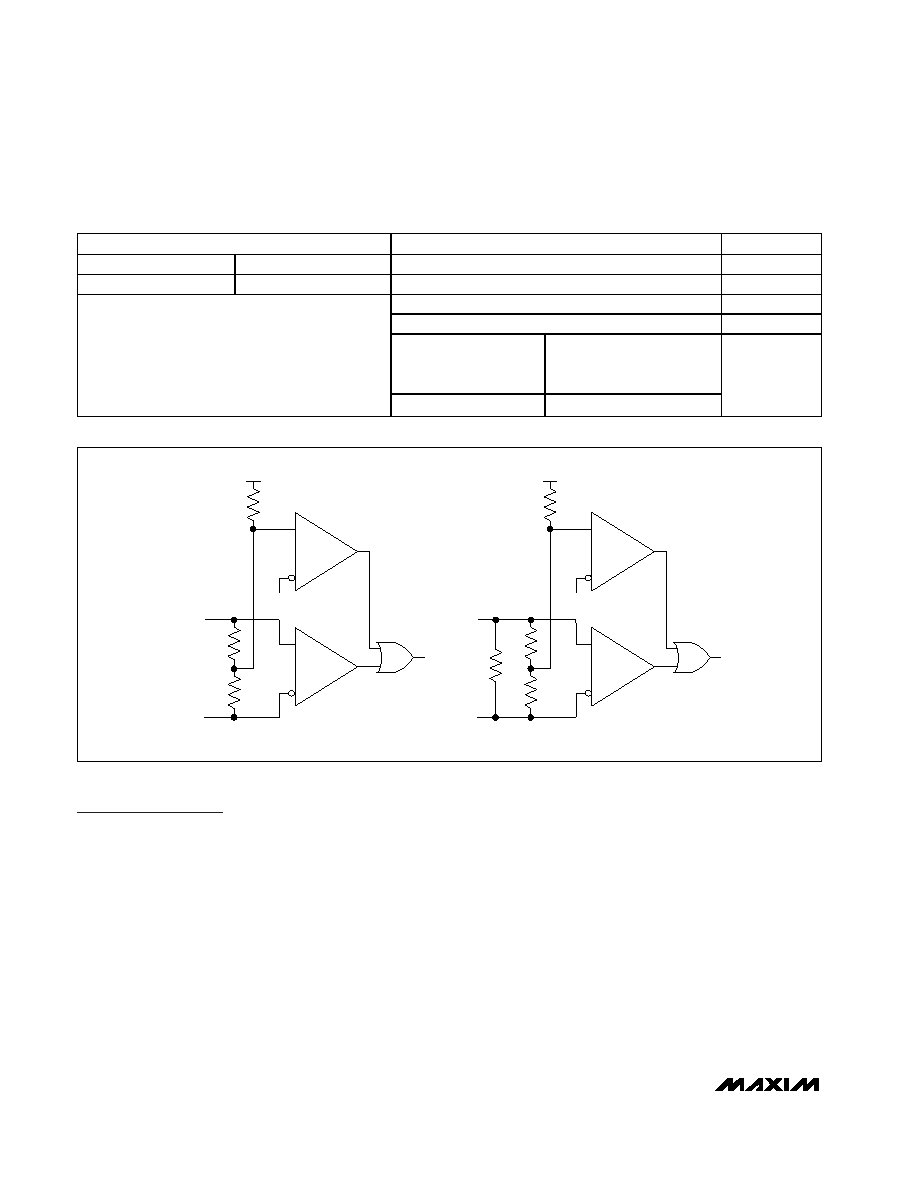

IN_+

VCC - 0.3V

IN_-

OUT_

MAX9125

MAX9126

RIN2

VCC

RIN1

IN_+

VCC - 0.3V

IN_-

OUT_

RIN2

VCC

RIN1

RDIFF

RIN1

Figure 1. Inputs with Internal Fail-Safe Circuitry

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VI-B02-MX-F1 | CONVERTER MOD DC/DC 15V 75W |

| MAX218CPP+ | IC TXRX RS232 DUAL 120KBPS 20DIP |

| IL3222-3E | TXRX ISO BUS 5MBPS RS422 16SOIC |

| VI-B01-MX-F4 | CONVERTER MOD DC/DC 12V 75W |

| UP050CH4R7K-KFC | CAP CER 4.7PF 50V 10% AXIAL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX9125ESE+ | 功能描述:LVDS 接口集成電路 Quad LVDS Line Driver RoHS:否 制造商:Texas Instruments 激勵(lì)器數(shù)量:4 接收機(jī)數(shù)量:4 數(shù)據(jù)速率:155.5 Mbps 工作電源電壓:5 V 最大功率耗散:1025 mW 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-16 Narrow 封裝:Reel |

| MAX9125ESE+T | 功能描述:LVDS 接口集成電路 Quad LVDS Line Driver RoHS:否 制造商:Texas Instruments 激勵(lì)器數(shù)量:4 接收機(jī)數(shù)量:4 數(shù)據(jù)速率:155.5 Mbps 工作電源電壓:5 V 最大功率耗散:1025 mW 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-16 Narrow 封裝:Reel |

| MAX9125ESE-T | 功能描述:LVDS 接口集成電路 RoHS:否 制造商:Texas Instruments 激勵(lì)器數(shù)量:4 接收機(jī)數(shù)量:4 數(shù)據(jù)速率:155.5 Mbps 工作電源電壓:5 V 最大功率耗散:1025 mW 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-16 Narrow 封裝:Reel |

| MAX9125EUE | 制造商:Maxim Integrated Products 功能描述:QUAD LVDS LINE RECEIVER - Bulk |

| MAX9126 | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:Quad LVDS Line Receivers with Integrated Termination |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。