- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384667 > MAX3878EHJ (MAXIM INTEGRATED PRODUCTS INC) 2.5Gbps, +3.3V Clock and Data Retiming ICs with Vertical Threshold Adjust PDF資料下載

參數(shù)資料

| 型號(hào): | MAX3878EHJ |

| 廠商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | 2.5Gbps, +3.3V Clock and Data Retiming ICs with Vertical Threshold Adjust |

| 中文描述: | CLOCK RECOVERY CIRCUIT, PQFP32 |

| 封裝: | 5 X 5 MM, 1 MM HEIGHT, EXPOSED PAD, TQFP-32 |

| 文件頁數(shù): | 11/16頁 |

| 文件大小: | 550K |

| 代理商: | MAX3878EHJ |

M

2.5Gbps, +3.3V Clock and Data Retiming ICs

with Vertical Threshold Adjust

______________________________________________________________________________________

11

Design Procedure

Setting the Loop Filter

The MAX3877/MAX3878 are designed for both regenera-

tor and receiver applications. The fully integrated PLL is a

classic second-order feedback system, with a loop band-

width (f

L

) fixed at 1.4MHz. The external capacitor, C

F

,

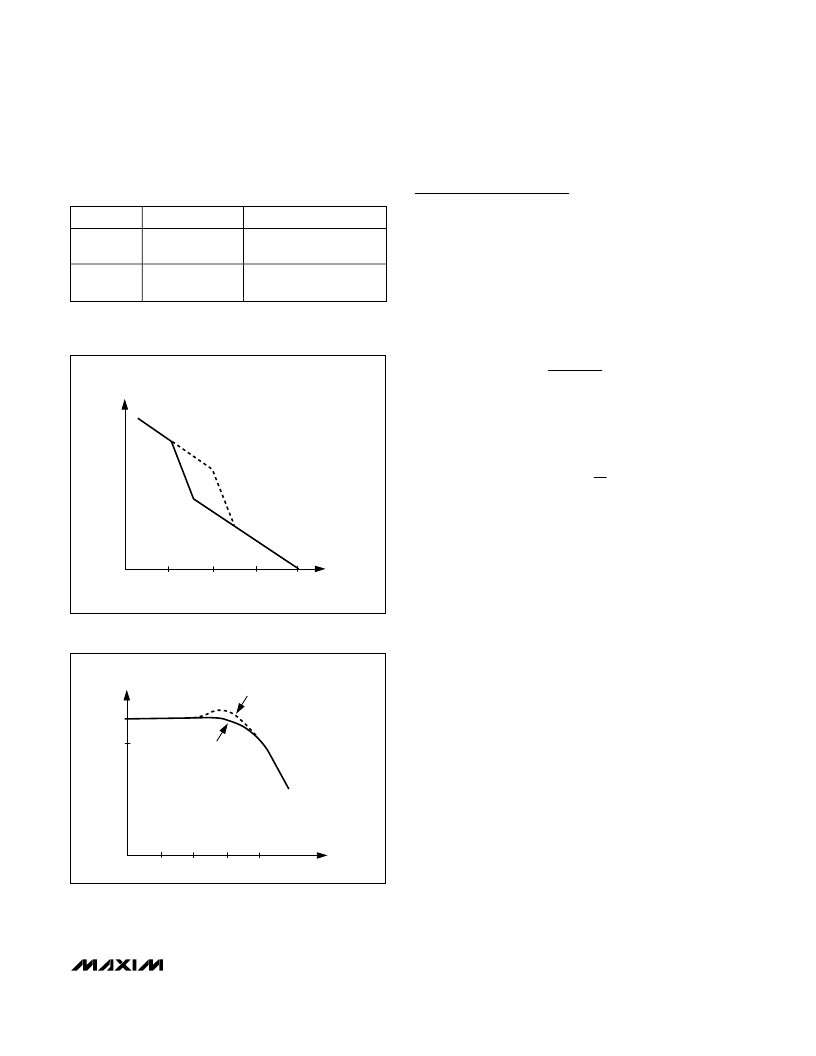

can be adjusted to set the loop damping. Figures 8 and 9

show the open-loop and closed-loop transfer functions.

The PLL zero frequency, f

Z

, is a function of external

capacitor C

F

, and can be approximated according to:

For an overdamped system (f

Z

/ f

L

< 0.25), the jitter peak-

ing (M

P

) of a second-order system can be approximated

by:

For example, using C

F

= 0.1μF results in a jitter peaking

of 0.16dB. Reducing C

F

below 0.01μF may result in PLL

instability. The recommended value of C

F

= 1.0μF is to

guarantee a maximum jitter peaking of less than 0.1dB.

C

F

must be a low-TC, high-quality capacitor of type XR7

or better.

Input Termination

Inputs for the MAX3877/MAX3878 are current-mode logic

(CML) compatible. The inputs all provide internal 50

ter-

mination to reduce the required number of external com-

ponents. When interfacing to differential PECL levels, it is

important to attenuate the signal while maintaining a 50

termination (see Figure 10). AC-coupling is also neces-

sary to maintain the input common-mode level.

Output Termination (MAX3877)

The MAX3877 uses current-mode logic (CML) for its high-

speed digital outputs. CML outputs are 50

back-termi-

nated, reducing the external component count. Refer to

Figure 11 for the output structure. CML outputs may be

terminated by 50

to V

CC

, or by 100

differential imped-

ance.

Output Termination (MAX3878)

The MAX3878 uses positive emitter-coupled logic (PECL)

for its high-speed outputs. PECL outputs are designed to

be terminated by 50

to (V

CC

- 2V). Refer to Applications

Note HFAN 0.1.0,

Interfacing Between CML, PECL, and

LVDS

, for more information.

M

f

f

P

Z

L

=

+

20

1

log

f

F

Z

C

)

=

1

2 60

(

C

F

= 1.0

μ

F

f

Z

= 2.6kHz

C

F

= 0.1

μ

F

f

Z

= 26kHz

H

O

(j2

π

f) (dB)

O

1000

f (kHz)

100

10

1

Figure 8. Open-Loop Transfer Function

C

F

= 1.0

μ

F

H(j2

π

f) (dB)

1000

100

10

1

f (kHz)

-3

0

C

C

F

= 0.1

μ

F

Figure 9. Closed-Loop Transfer Function

SIS = 0

SIS = 1

LREF = 0

SDI

(Normal Operation)

SLBI

(System Loopback Mode)

LREF = 1

SLBI

(Holdover Mode)

SLBI

(Holdover Mode)

Table 1. Selecting Input Path

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAX3890 | Full-Duplex LVDM Transceiver 8-MSOP -40 to 85 |

| MAX3890ECB | +3.3V, 2.5Gbps, SDH/SONET 16:1 Serializer with Clock Synthesis and LVDS Inputs |

| MAX3935EGJ | 10.7Gbps EAM Driver |

| MAX3935 | 10.7Gbps EAM Driver |

| MAX3941 | 10Gbps EAM Driver with Integrated Bias Network |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX3878EHJ-T | 功能描述:計(jì)時(shí)器和支持產(chǎn)品 2.5Gbps 3.3V Clock & Data Retiming IC RoHS:否 制造商:Micrel 類型:Standard 封裝 / 箱體:SOT-23 內(nèi)部定時(shí)器數(shù)量:1 電源電壓-最大:18 V 電源電壓-最小:2.7 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝:Reel |

| MAX3878EVKIT | 功能描述:計(jì)時(shí)器和支持產(chǎn)品 Evaluation Kit for the MAX3877 MAX3878 RoHS:否 制造商:Micrel 類型:Standard 封裝 / 箱體:SOT-23 內(nèi)部定時(shí)器數(shù)量:1 電源電壓-最大:18 V 電源電壓-最小:2.7 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝:Reel |

| MAX3880ECB | 制造商:Rochester Electronics LLC 功能描述: 制造商:Maxim Integrated Products 功能描述: |

| MAX3880ECB+ | 制造商:Maxim Integrated Products 功能描述:SDH/SONET1:16 DESERLIZER W/ CLOCK RECOVERY 64TQFP EP - Bulk |

| MAX3880ECB+D | 功能描述:串行器/解串器 - Serdes 3.3V 2.488Gbps SDH/ SONET 1:16 Deserial RoHS:否 制造商:Texas Instruments 類型:Deserializer 數(shù)據(jù)速率:1.485 Gbit/s 輸入類型:ECL/LVDS 輸出類型:LVCMOS 輸入端數(shù)量:1 輸出端數(shù)量:20 工作電源電壓:2.375 V to 2.625 V 工作溫度范圍:0 C to + 70 C 封裝 / 箱體:TQFP-64 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。