- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄385525 > MAX3301EEBA-T (MAXIM INTEGRATED PRODUCTS INC) CLAMP PDF資料下載

參數(shù)資料

| 型號(hào): | MAX3301EEBA-T |

| 廠(chǎng)商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類(lèi): | 通用總線(xiàn)功能 |

| 英文描述: | CLAMP |

| 中文描述: | LINE TRANSCEIVER, PBGA25 |

| 封裝: | 5 X 5 MM, UCSP-25 |

| 文件頁(yè)數(shù): | 25/33頁(yè) |

| 文件大小: | 935K |

| 代理商: | MAX3301EEBA-T |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)當(dāng)前第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)

M

USB On-the-Go Transceiver and Charge Pump

______________________________________________________________________________________

25

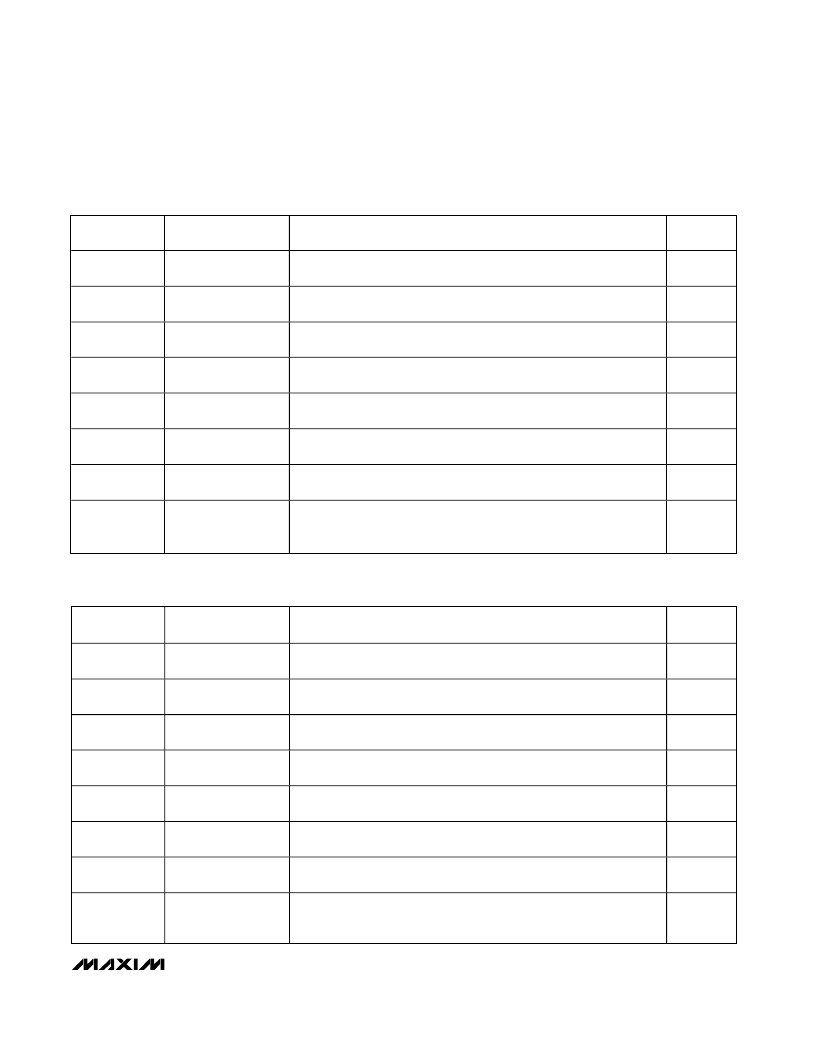

BIT NUMBER

SYMBOL

CONTENTS

VALUE AT

POWER-UP

0

vbus_vld

S et to 0 to d sab e the vb us_vld i nter up for a hig h- o- ow transiti on. S et to 1 to

enab e the vb us_vld i nter up for a hig h- o- ow transiti on. S ee Tab es 10 and 11.

0

1

sess_vld

S et to 0 to d sab e the sess_vld i nter up for a hig h- o- ow transiti on. S et to 1 to

enab e the sess_vld i nter up for a hig h- o- ow transiti on. S ee Tab es 10 and 11.

0

2

dp_hi

S et to 0 to d sab e the d p _hi interr up for a hi g h-to- ow tr ansi i on. Set to 1 to

enab e the d p _hi interr up for a hi g h-to- ow tr ansi i on. See Tab es 10 and 11.

0

3

id_gnd

S et to 0 to d sab e the i d _g nd i nter upt for a hi g h- o-l ow tr ansi ion. S et to 1 to

enab e the i d _g nd i nter upt for a hi g h- o-l ow tr ansi ion. S ee Tab es 10 and 11.

0

4

dm_hi

S et to 0 to d sab e the d m _hi interr up for a hi g h-to- ow tr ansi i on. Set to 1 to

enab e the d m _hi interr up for a hi g h-to- ow tr ansi i on. See Tab es 10 and 11.

0

5

id_float

S et to 0 to d sab e the i d _fl oat i nter up for a hig h- o- ow transiti on. S et to 1 to

enab e the i d _fl oat i nter up for a hig h- o- ow transiti on. S ee Tab es 10 and 11.

0

6

bdis_acon

S et to 0 to d sab e the b d s_acon interr up for a hi g h-to- ow tr ansi i on. Set to 1 to

enab e the b d s_acon interr up for a hi g h-to- ow tr ansi i on. See Tab es 10 and 11.

0

7

cr_int_sess_end

S et to 0 to d sab e the cr _i nt_sess_end i nter up for a hi g h- o- ow tr ansi i on.

S et to 1 to enab e the cr _i nt_sess_end i nter up for a hi g h- o- ow tr ansi i on.

S ee Tab es 10 and 11.

0

Table 12. Interrupt-Enable Low Register (Write to Address 0Ch to Set, Write to Address

0Dh to Clear)

BIT NUMBER

SYMBOL

CONTENTS

VALUE AT

POWER-UP

0

vbus_vld

S et to 0 to d sab e the vb us_vld i nter up for a l ow o- hi gh transiti on. S et to 1 to

enab e the vb us_vld i nter up for a l ow o- hi gh transiti on. S ee Tab es 10 and 11.

0

1

sess_vld

S et to 0 to d sab e the sess_vld i nter up for a l ow o- hi gh transiti on. S et to 1 to

enab e the sess_vld i nter up for a l ow o- hi gh transiti on. S ee Tab es 10 and 11.

0

2

dp_hi

S et to 0 to d sab e the d p _hi i nter up for a l ow o- hi g h tr ansi i on. S et to 1 to

enab e the d p _hi i nter up for a l ow o- hi g h tr ansi i on. S ee Tab es 10 and 11.

0

3

id_gnd

S et to 0 to d sab e the i d _g nd i nter up for a l ow o- hi g h tr ansi i on. S et to 1 to

enab e the i d _g nd i nter up for a l ow o- hi g h tr ansi i on. S ee Tab es 10 and 11.

0

4

dm_hi

S et to 0 to d sab e the d m _hi i nter up for a l ow o- hi g h tr ansi i on. S et to 1 to

enab e the d m _hi i nter up for a l ow o- hi g h tr ansi i on. S ee Tab es 10 and 11.

0

5

id_float

S et to 0 to d sab e the i d _fl oat i nter up for a l ow o- hi g h tr ansi i on. S et to 1 to

enab e the i d _fl oat i nter up for a l ow o- hi g h tr ansi i on. S ee Tab es 10 and 11.

0

6

bdis_acon

S et to 0 to d sab e the b d s_acon interr up for a low o- hig h tr ansi i on. Set to 1 to

enab e the b d s_acon interr up for a low o- hig h tr ansi i on. See Tab es 10 and 11.

0

7

cr_int_sess_end

S et to 0 to d sab e the cr _i nt_sess_end i nter up for a l ow o- hi g h tr ansi i on.

S et to 1 to enab e the cr _i nt_sess_end i nter up for a l ow o- hi g h tr ansi i on.

S ee Tab es 10 and 11.

0

Table 13. Interrupt-Enable High Register (Write to Address 0Eh to Set, Write to Address

0Fh to Clear)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAX3301EETJ | CLAMP |

| MAX333A | Precision, Quad, SPDT, CMOS Analog Switch(MAX333的改進(jìn)型,低導(dǎo)通電阻模擬開(kāi)關(guān)) |

| MAX333 | High Speed Quad SPST Analog Switches(接通電阻175Ω,漏電流5nA,導(dǎo)通速率1000ns,單刀單擲模擬開(kāi)關(guān)) |

| MAX334EJE | High Speed Quad SPST Analog Switch |

| MAX334EWE | High Speed Quad SPST Analog Switch |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX3301EETI+ | 制造商:Maxim Integrated Products 功能描述:USB ON-THE-GO TRANSCEIVERS AND CHARGE PUMPS - Rail/Tube |

| MAX3301EETJ | 功能描述:USB 接口集成電路 RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類(lèi)型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

| MAX3301EETJ+ | 功能描述:USB 接口集成電路 USB On-the-Go Tcvr & Charge Pump RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類(lèi)型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

| MAX3301EETJ+GH7 | 功能描述:USB 接口集成電路 USB On-the-Go Transceiver and Charge Pump RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類(lèi)型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

| MAX3301EETJ+T | 功能描述:USB 接口集成電路 USB On-the-Go Tcvr & Charge Pump RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類(lèi)型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。