- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385523 > MAX2370_1 (Maxim Integrated Products, Inc.) Evaluation Kit PDF資料下載

參數(shù)資料

| 型號: | MAX2370_1 |

| 廠商: | Maxim Integrated Products, Inc. |

| 英文描述: | Evaluation Kit |

| 中文描述: | 評估板 |

| 文件頁數(shù): | 4/11頁 |

| 文件大?。?/td> | 865K |

| 代理商: | MAX2370_1 |

E

RF Upconverter Evaluation

1) Connect a CDMA RF signal generator to the IFIN

port using the SMA connector. Set the carrier fre-

quency to 120MHz, set the output power to

-16.5dBm, and set the modulation to reverse-chan-

nel CDMA.

2) Connect RFL to the spectrum analyzer. Configure

the spectrum analyzer to measure ACPR for

reverse-channel CDMA. Set the center frequency to

455MHz with a +10dBm reference level and 30kHz

resolution bandwidth.

3) Set the V

GC

voltage to 2.5V and adjust the IF input

power until the RF output power is +8dBm. The

ACPR at ±885kHz offset will be approximately

-67dBc, and the ACPR at ±1.98MHz will be approx-

imately -86dBc.

Cascaded Evaluation

1) Connect the CDMA baseband signal generator to

the I and Q ports using BNC connectors. Set the

modulation to reverse-channel CDMA at a 780mV

P-P

output level. The nominal input level at the IC

’

s I/Q

input pins is 130mV

RMS

. Measure the differential

voltage at the chip

’

s I/Q inputs and adjust the signal

generator

’

s output if necessary to achieve

130mV

RMS

.

2) Connect an external 120MHz bandpass filter

between the IFOUT and IFIN ports of the MAX2370

evaluation kit. A 50

filter with approximately 4dB of

insertion loss is recommended, or an attenuator with

a loss of 4dB can be used if a 120MHz filter is not

available. The on-board baluns and matching net-

works at the IFOUT and IFIN ports each add approx-

imately 0.5dB of loss, for a total IF loss of 5dB.

3) Connect RFL to the spectrum analyzer. Configure

the spectrum analyzer to measure ACPR for

reverse-channel CDMA. Set the center frequency to

455MHz with a +10dBm reference level and 30kHz

resolution bandwidth.

4) Adjust the V

GC

voltage until the RF output power is

+8dBm. The ACPR at ±885kHz offset will be

approximately -64dBc, and the ACPR at ±1.98MHz

will be approximately -82dBc.

Adjustments and Control

VGA Adjust

Apply a voltage from 0.5V to 2.5V to header VGC to

adjust the IF and RF VGA of the MAX2370. The VGC

voltage is filtered on the EV kit to minimize undesired

amplitude modulation.

Interface Control

The interface port is designed to use a 20-pin ribbon

cable (Figure 1); 10 pins are signal lines, and the other

10 pins are digital grounds. Pin 1 of the interface cable

is red. Pin 1 is also designated in the silk screen on

each of the PC boards.

Detailed Description

The following section covers the EV kit

’

s circuit blocks

in detail (refer to the MAX2370 data sheet for additional

information).

I/Q Inputs

The single-ended I/Q signals are converted to differen-

tial by operational amplifiers on the EV kit. The op amps

also provide DC bias to the I/Q input pins of the

MAX2370. The EV kits are set up to provide 130mV

RMS

differential to the IC when driven with an IS-95 forward-

modulated source set to deliver 0.9V

P-P

into a matched

50

load.

Programming Interface

The programming interface is provided by the INTF2300

interface board. The interface board buffers and level

shifts logic levels from the PC to the MAX2370 EV kit

(refer to the INTF2300 documentation). These logic sig-

nals control the logic pins as well as the serial interface.

IFLO

The IFLO output port provides an output signal at the

IF VCO frequency with a typical -12dBm output power.

Enable the IFLO port by setting the BUF_EN bit in the

OPCTRL register.

REF

REF is the reference frequency input to the RF and IF PLL.

The REF port is AC-coupled. Make sure the reference sig-

nal has low phase noise, similar to that of a TCXO.

MAX2370 Evaluation Kit

4

_______________________________________________________________________________________

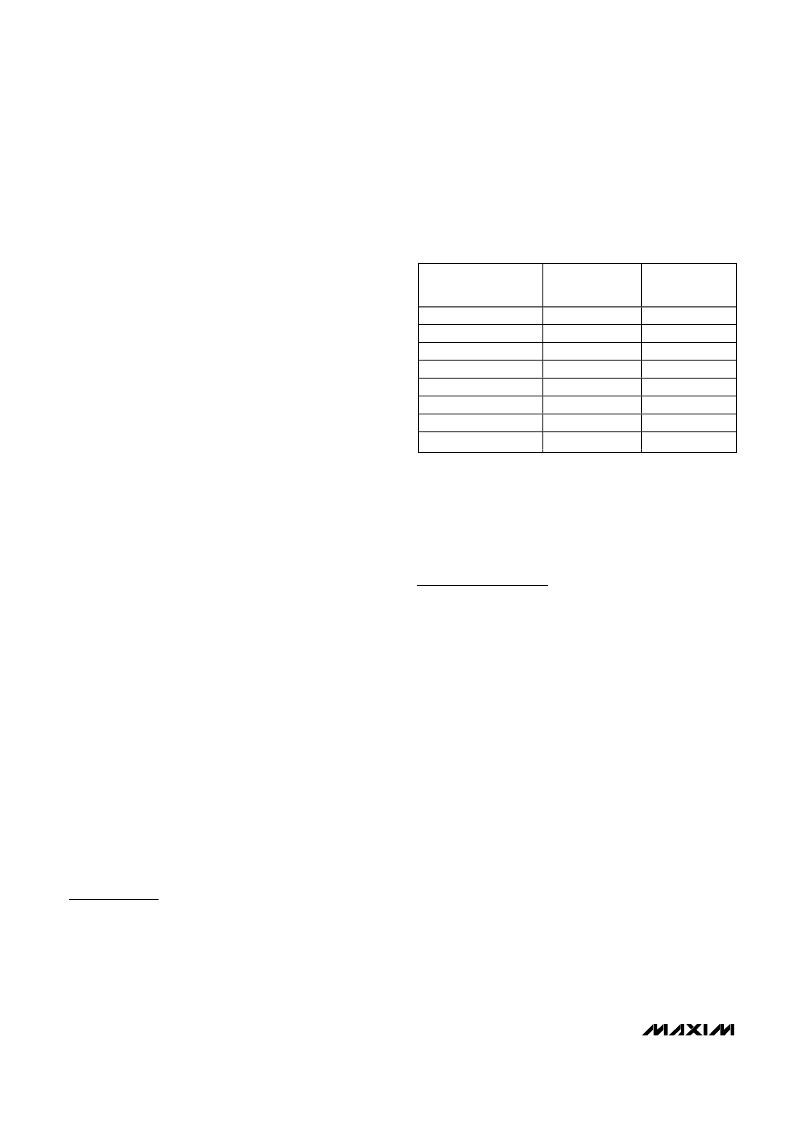

Table 1. Register Settings

REGISTER NAME

TYPICAL

REGISTER

SETTINGS

23000

DEC

384

DEC

4800

DEC

384

DEC

090F

HEX

D03F

HEX

0C38

HEX

100

HEX

REGISTER

ADDRESS

RFM[17:0]

RFR[12:0]

IFM[13:0]

IFR[10:0]

OPCTRL[15:0]

CONFIG[15:0]

I

CC

CTRL[15:0]

TEST[8:0]

0000

b

0001

b

0010

b

0011

b

0100

b

0101

b

0110

b

0111

b

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAX2370EVKIT | Evaluation Kit |

| MAX2370 | Complete 450MHz Quadrature Transmitter |

| MAX2370ETM | Complete 450MHz Quadrature Transmitter |

| MAX2371EGC | LNAs with Step Attenuator and VGA |

| MAX2371ETC | LNAs with Step Attenuator and VGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX2370ETM | 功能描述:射頻發(fā)射器 Complete 450MHz Quadrature Txr RoHS:否 制造商:Micrel 類型:ASK Transmitter 封裝 / 箱體:SOT-23-6 工作頻率:300 MHz to 450 MHz 封裝:Reel |

| MAX2370ETM+ | 功能描述:射頻發(fā)射器 Complete 450MHz Quadrature Txr RoHS:否 制造商:Micrel 類型:ASK Transmitter 封裝 / 箱體:SOT-23-6 工作頻率:300 MHz to 450 MHz 封裝:Reel |

| MAX2370ETM+T | 功能描述:射頻發(fā)射器 Complete 450MHz Quadrature Txr RoHS:否 制造商:Micrel 類型:ASK Transmitter 封裝 / 箱體:SOT-23-6 工作頻率:300 MHz to 450 MHz 封裝:Reel |

| MAX2370ETM-T | 功能描述:射頻發(fā)射器 Complete 450MHz Quadrature Txr RoHS:否 制造商:Micrel 類型:ASK Transmitter 封裝 / 箱體:SOT-23-6 工作頻率:300 MHz to 450 MHz 封裝:Reel |

| MAX2370EVKIT | 功能描述:射頻開發(fā)工具 MAX2370 Eval Kit RoHS:否 制造商:Taiyo Yuden 產(chǎn)品:Wireless Modules 類型:Wireless Audio 工具用于評估:WYSAAVDX7 頻率: 工作電源電壓:3.4 V to 5.5 V |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。