- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384650 > MAX1428ETN (MAXIM INTEGRATED PRODUCTS INC) 15-Bit, 80Msps ADC with -78.4dBFS Noise Floor for IF Applications PDF資料下載

參數(shù)資料

| 型號(hào): | MAX1428ETN |

| 廠商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類: | ADC |

| 英文描述: | 15-Bit, 80Msps ADC with -78.4dBFS Noise Floor for IF Applications |

| 中文描述: | 1-CH 15-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, QCC56 |

| 封裝: | 8 X 8 MM, 0.80 MM HEIGHT, MO-220WLLD-5, TQFN-56 |

| 文件頁(yè)數(shù): | 4/18頁(yè) |

| 文件大?。?/td> | 717K |

| 代理商: | MAX1428ETN |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)

M

15-Bit, 80Msps ADC with -78.4dBFS

Noise Floor for IF Applications

4

_______________________________________________________________________________________

Note 1:

Dynamic performance is based on a 32,768-point data record with a sampling frequency of f

SAMPLE

= 80.019456MHz, an

input frequency of f

IN

= f

SAMPLE

x (28667/32768) = 70.004814MHz, and a frequency bin size of 2442Hz. Close-in (f

IN

±29.3kHz) and low-frequency (DC to 58.6kHz) bins are excluded from the spectrum analysis.

Note 2:

Apply the same voltage levels to DV

CC

and DRV

CC

.

Note 3:

Guaranteed by design and characterization.

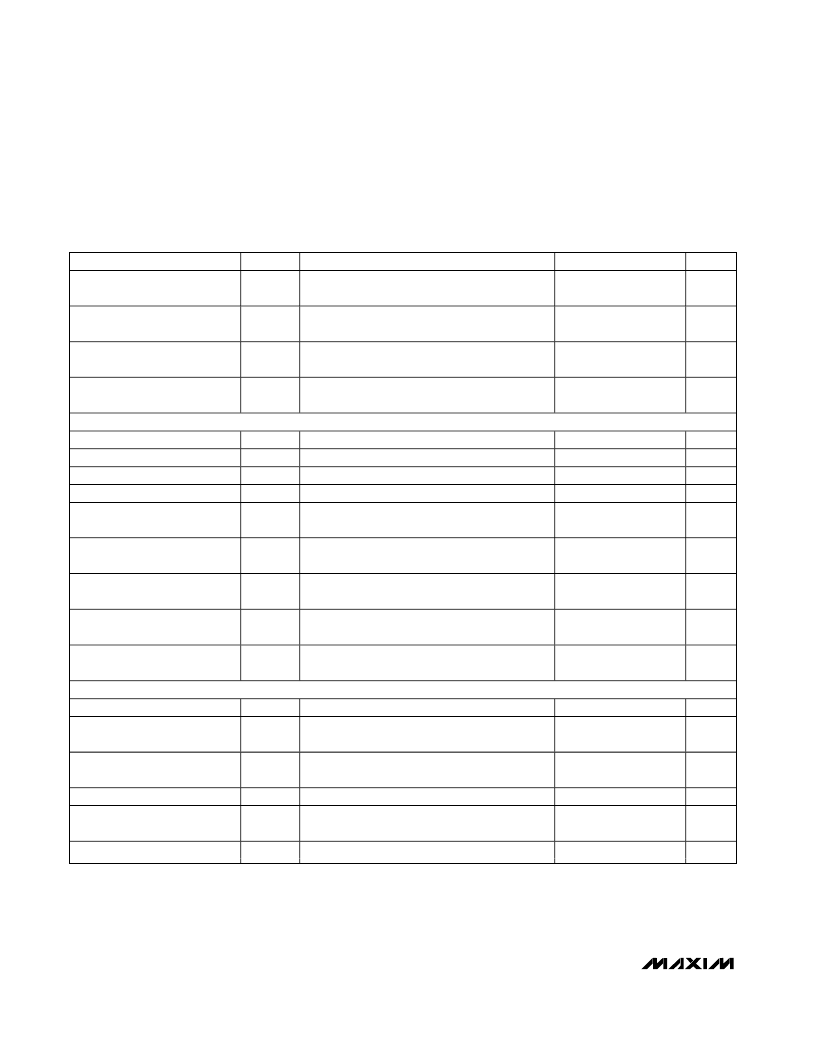

ELECTRICAL CHARACTERISTICS (continued)

(AV

CC

= 5V, DV

CC

= DRV

CC

= 2.5V, GND = 0, INP and INN driven differentially with -2dBFS, CLKP and CLKN driven differentially

with a 2V

P-P

sinusoidal input signal, C

L

= 5pF at digital outputs, f

CLK

= 80MHz, T

A

= T

MIN

to T

MAX

, unless otherwise noted. Typical

values are at T

A

= +25°C, unless otherwise noted.

≥

+25°C guaranteed by production test, <+25°C guaranteed by design and char-

acterization.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

CLKP Rising Edge to

DATA Not Valid

t

DNV

(Note 3)

2.6

3.8

5.7

ns

CLKP Rising Edge to

DATA Valid (Guaranteed)

t

DGV

(Note 3)

3.4

5.2

8.6

ns

DATA Setup Time

(Before DAV Rising Edge)

t

SETUP

(Note 3)

t

CLKP

-

0.5

t

CLKP

+ 1.3

t

CLKP

+ 2.4

ns

DATA Hold Time

(After DAV Rising Edge)

t

HOLD

(Note 3)

t

CLKN

-

3.6

t

CLKN

- 2.8

t

CLKN

- 2.0

ns

TIMING CHARACTERISTICS (DV

CC

= DRV

CC

= 3.3V)

CLKP/CLKN Duty Cycle

Effective Aperture Delay

Output Data Delay

Data Valid Delay

Duty

50 ±5

230

4.1

6.3

%

ps

ns

ns

t

AD

t

DAT

t

DAV

(Note 3)

(Note 3)

2.8

5.3

6.5

8.6

Pipeline Latency

t

LATENCY

3

Clock

Cycles

CLKP Rising Edge to

DATA Not Valid

t

DNV

(Note 3)

2.5

3.4

5.2

ns

CLKP Rising Edge to

DATA Valid (Guaranteed)

t

DGV

(Note 3)

3.2

4.4

7.4

ns

DATA Setup Time

(Before DAV Rising Edge)

t

SETUP

(Note 3)

t

CLKP

+ 0.2

t

CLKP

+ 1.7

t

CLKP

+ 2.8

ns

DATA Hold Time

(After DAV Rising Edge)

t

HOLD

(Note 3)

t

CLKN

-

3.5

t

CLKN

- 2.7

t

CLKN

- 2.0

ns

POWER REQUIREMENTS

Analog-Supply Voltage Range

AV

CC

5 ±3%

V

Digital-Supply Voltage Range

DV

CC

(Note 2)

2.3 to

3.5

V

Output-Supply Voltage Range

DRV

CC

(Note 2)

2.3 to

3.5

V

Analog Supply Current

I

AVCC

I

DVCC

+

I

DRVCC

PDISS

400

450

mA

Digital + Output Supply Current

f

CLK

= 80MHz, C

L

= 5pF

38

44

mA

Total Power Dissipation

2095

mW

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAX1458 | 1%-Accurate, Digitally Trimmed Sensor Signal Conditioner |

| MAX1458AAE | 1%-Accurate, Digitally Trimmed Sensor Signal Conditioner |

| MAX1458CAE | 1%-Accurate, Digitally Trimmed Sensor Signal Conditioner |

| MAX1459 | 2-Wire, 4-20mA Smart Signal Conditioner |

| MAX1459AAP | 2-Wire, 4-20mA Smart Signal Conditioner |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX1428ETN+ | 制造商:Maxim Integrated Products 功能描述:- Rail/Tube |

| MAX1428ETN+TD | 制造商:Maxim Integrated Products 功能描述:ADC SGL PIPELINED 80MSPS 15-BIT PARALLEL 56TQFN EP - Tape and Reel |

| MAX1428ETN-D | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| MAX1428ETN-TD | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| MAX1429ETN+ | 制造商:Maxim Integrated Products 功能描述:- Rail/Tube |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。