- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384641 > M5M5T5636UG-25 (Mitsubishi Electric Corporation) RECTIFIER SCHOTTKY SINGLE 1A 40V 45A-Ifsm 0.53Vf 0.1A-IR SMB 3K/REEL PDF資料下載

參數(shù)資料

| 型號: | M5M5T5636UG-25 |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | RECTIFIER SCHOTTKY SINGLE 1A 40V 45A-Ifsm 0.53Vf 0.1A-IR SMB 3K/REEL |

| 中文描述: | 18874368位(524288 - Word的36位)網(wǎng)絡(luò)的SRAM |

| 文件頁數(shù): | 1/23頁 |

| 文件大小: | 287K |

| 代理商: | M5M5T5636UG-25 |

MITSUBISHI LSIs

M5M5T5636UG – 25,22,20

18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM

1

MITSUBISHI

ELECTRIC

Advanced Information

M5M5T5636UG REV.0.1

DESCRIPTION

The M5M5T5636UG is a family of 18M bit synchronous SRAMs

organized as 524288-words by 36-bit. It is designed to eliminate

dead bus cycles when turning the bus around between reads and

writes, or writes and reads. Mitsubishi's SRAMs are fabricated

with high performance, low power CMOS technology, providing

greater reliability. M5M5T5636UG operates on 2.5V power/ 1.8V

I/O supply or a single 2.5V power supply and are 2.5V CMOS

compatible.

FEATURES

Fully registered inputs and outputs for pipelined operation

Fast clock speed: 250, 225, and 200 MHz

Fast access time: 2.6, 2.8, 3.2 ns

Single 2.5V -5% and +5% power supply V

DD

Separate V

DDQ

for 2.5V or 1.8V I/O

Individual byte write (BWa# - BWd#) controls may be tied

LOW

Single Read/Write control pin (W#)

CKE# pin to enable clock and suspend operations

Internally self-timed, registers outputs eliminate the need to

control G#

Snooze mode (ZZ) for power down

Linear or Interleaved Burst Modes

Three chip enables for simple depth expansion

JTAG boundary scan support

Package

165(11x15) bump BGA

Body Size (13mm x 15mm)

Bump Pitch 1.0mm

APPLICATION

High-end networking products that require high bandwidth, such

as switches and routers

.

FUNCTION

Synchronous circuitry allows for precise cycle control

triggered by a positive edge clock transition.

Synchronous signals include : all Addresses, all Data Inputs, all

Chip Enables (E1#, E2, E3#), Address Advance/Load (ADV),

Clock Enable (CKE#), Byte Write Enables (BWa#, BWb#, BWc#,

BWd#) and Read/Write (W#). Write operations are controlled by

the four Byte Write Enables (BWa# - BWd#) and Read/Write(W#)

inputs. All writes are conducted with on-chip synchronous self-

timed write circuitry.

Asynchronous inputs include Output Enable (G#), Clock (CLK)

and Snooze Enable (ZZ). The HIGH input of ZZ pin puts the

SRAM in the power-down state.The Linear Burst order (LBO#) is

DC operated pin. LBO# pin will allow the choice of either an

interleaved burst, or a linear burst.

All read, write and deselect cycles are initiated by the ADV

LOW input. Subsequent burst address can be internally

generated as controlled by the ADV HIGH input.

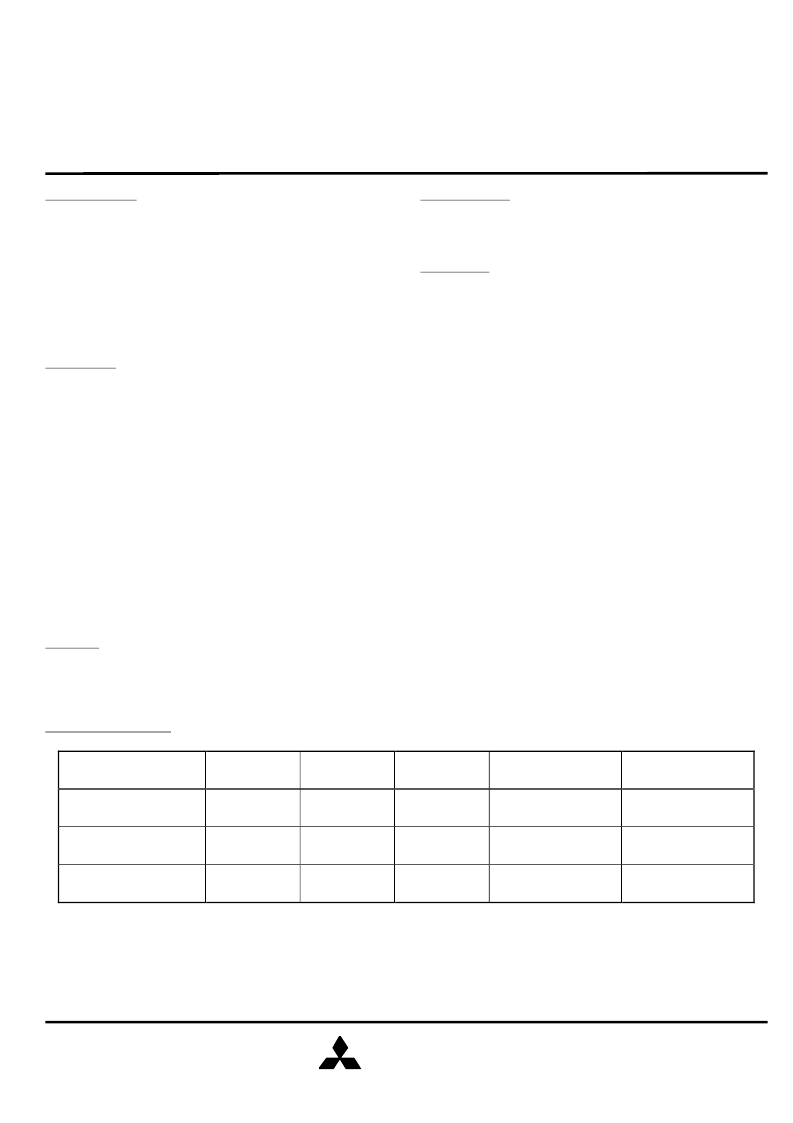

PART NAME TABLE

Part Name

Frequency

Access

Cycle

Active Current

(max.)

Standby Current

(max.)

M5M5T5636UG - 25

250MHz

2.6ns

4.0ns

400mA

20mA

M5M5T5636UG - 22

225MHz

2.8ns

4.4ns

380mA

20mA

M5M5T5636UG - 20

200MHz

3.2ns

5.0ns

360mA

20mA

2001.March Rev.0.1

Advanced Information

Notice: This is not final specification.

Some parametric limits are subject to change.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M5M5T5636GP-20 | 18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM |

| M5M5W416CWG-85HI | 4194304-BIT (262144-WORD BY 16-BIT) CMOS STATIC RAM |

| M61311SP | I2C BUS CONTROLLED VIDEO PRE-AMP FOR HIGH RESOLUTION COLOR DISPLAY |

| M61316SP | I2C BUS CONTROLLED VIDEO PRE-AMP FOR HIGH RESOLUTION COLOR DISPLAY |

| M61506FP | Peak hold IC for 5 band spectrum analyzer displays |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M5M5T5672TG | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:18874368-BIT(262144-WORD BY 72-BIT) NETWORK SRAM |

| M5M5T5672TG-20 | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:18874368-BIT(262144-WORD BY 72-BIT) NETWORK SRAM |

| M5M5T5672TG-22 | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:18874368-BIT(262144-WORD BY 72-BIT) NETWORK SRAM |

| M5M5T5672TG-25 | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:18874368-BIT(262144-WORD BY 72-BIT) NETWORK SRAM |

| M5M5V108CFP-10H | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:1048576-BIT(131072-WORD BY 8-BIT)CMOS STATIC RAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。