- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45035 > M37545G8-XXXGP 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQFP32 PDF資料下載

參數(shù)資料

| 型號: | M37545G8-XXXGP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQFP32 |

| 封裝: | 7 X 7 MM, 0.80 MM PITCH, PLASTIC, LQFP-32 |

| 文件頁數(shù): | 58/63頁 |

| 文件大?。?/td> | 774K |

| 代理商: | M37545G8-XXXGP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁當前第58頁第59頁第60頁第61頁第62頁第63頁

(1/2)

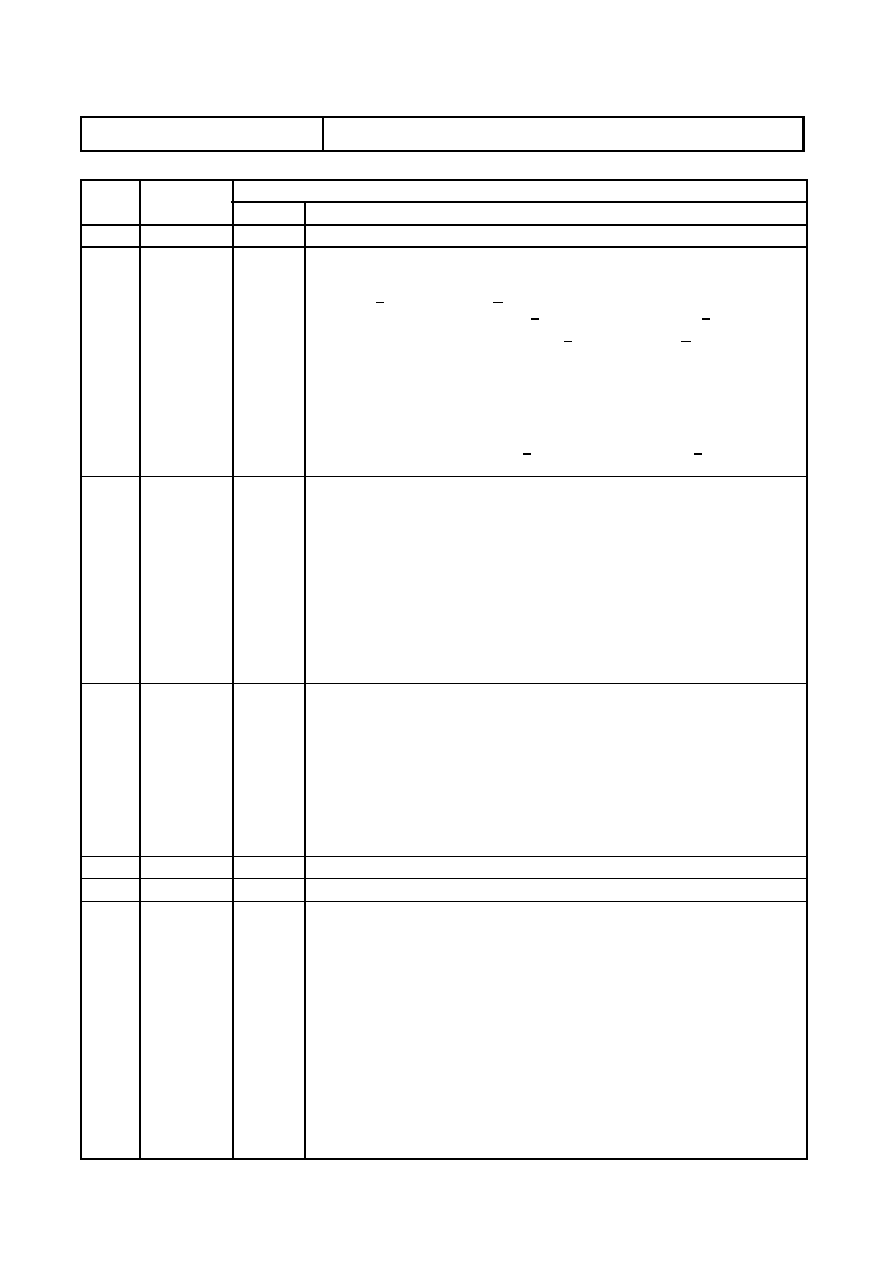

REVISION HISTORY

7545 Group Datasheet

Rev.

Date

Description

Page

Summary

1.00

Feb. 07, 2005

First edition issued

1.01

May. 10, 2005

20

Fig.22 : Carrier wave auto-control bit; “1” and “0” added.

26

Standard operation of watchdog timer and Operation of STP instruction disable bit:

address FFFA16

→ address FFDA16

Note on Watchdog Timer 2: ... set to “1” just before ...

→ ... set to “0” just before ...

28

Voltage Drop Detection Circuit: address FFFA16

→ address FFDA16

33

State transition deleted

36

Fig. 51 partly revised

40

Table 9: RPL; V

→ k

42

Fig. 55: CNTR0

→ INT0

47

Notes on Watchdog timer: ... set to “1” just before ...

→ ... set to “0” just before ...

Notes on Clock Generating Circuit 1: bits 2 to 4 to 7

→ bits 2, 6, 7

1.02

Jul. 20, 2005

All pages ROM option

→ Function set ROM

3

Table 1: added.

11

ROM Code Protect Address (address FFDB16) added.

16

Termination of unused pins added.

35

[ROM option data] ROMOP

→ [Function set ROM] FSROM

Fig. 42, 43: partly revised.

37

(4) Wiring to CNVSS pin

→ (4) Wiring to VPP pin

51

DATA REQUIRED FOR QzROM WRITING ORDERS, Notes On QzROM Writing

Orders,

Notes On ROM Code Protect added.

1.03

Oct. 21, 2005

STP instruction disable bit

→ STP instruction function selection bit

29

“Operation of STP instruction function selection bit” revised.

30

Fig.33 Block diagram of watchdog timer and reset circuit

“Count start (Watchdog timer disable bit (bit 0 of FSROM))” added.

35

Function set ROM : Description revised.

Fig.42: Reserved

→ Renesas shipment test area

“When the checksum is included in the user program, avoid assigning it to

these areas.” added to Note.

Fig.43: Bit 0, bit 1 and bit 4 of FSROM revised.

1.04

May. 17, 2006

“PRELIMINARY” eliminated.

1.05

May. 18, 2006

6

Fig.4 “Under development” eliminated.

1.06

Feb. 29, 2008

1

Revised by additional new products (memory size)

2

Fig. 2 is added

3

Revised by additional new products (memory size and package)

6

Fig. 5 is added

8

Revised by additional new products (memory size, package, Fig. 6, and Table 4)

12

Fig. 9 is revised

13

Function set ROM Area and Notes (2) - (5) added

Clock circuit is deleted from [Function set ROM data] FSROM

Notes on use deleted

14

Fig. 10 is revised

16

Fig.12 added

20 to 24

Interrupts is revised whole

相關PDF資料 |

PDF描述 |

|---|---|

| M37545GC-XXXGP | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQFP32 |

| M37545G1KP | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PDSO32 |

| M37545G4GP | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQFP32 |

| M37545G6KP | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PDSO32 |

| M37545G6-XXXGP | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQFP32 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| M37545GCGP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37545GCKP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37545GC-XXXGP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37545GFGP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37545GFKP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

發(fā)布緊急采購,3分鐘左右您將得到回復。