- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370825 > M2S12D30TP-10L (Mitsubishi Electric Corporation) 128 x 64 pixel format, LED Backlight available PDF資料下載

參數(shù)資料

| 型號: | M2S12D30TP-10L |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | 128 x 64 pixel format, LED Backlight available |

| 中文描述: | 512M雙數(shù)據(jù)速率同步DRAM |

| 文件頁數(shù): | 38/38頁 |

| 文件大小: | 754K |

| 代理商: | M2S12D30TP-10L |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁當前第38頁

MITSUBISHI

ELECTRIC

-38-

M2S12D20/ 30TP -75, -75L, -10, -10L

512M Double Data Rate Synchronous DRAM

Feb. '02

MITSUBISHI LSIs

DDR SDRAM (Rev.1.1)

MITSUBISHI ELECTRIC

Revision History

Rev. 1.0

Nov ’01

-New registration

Rev. 1.1

Jan ’02

-Added -75L,-10L spec.

-Added WRITEA and READA operating description table when new command asserted

-Deleted -75A spec.

-Added AC overshoot and overshoot spec.

-Changed the average supply current from Vdd spec.

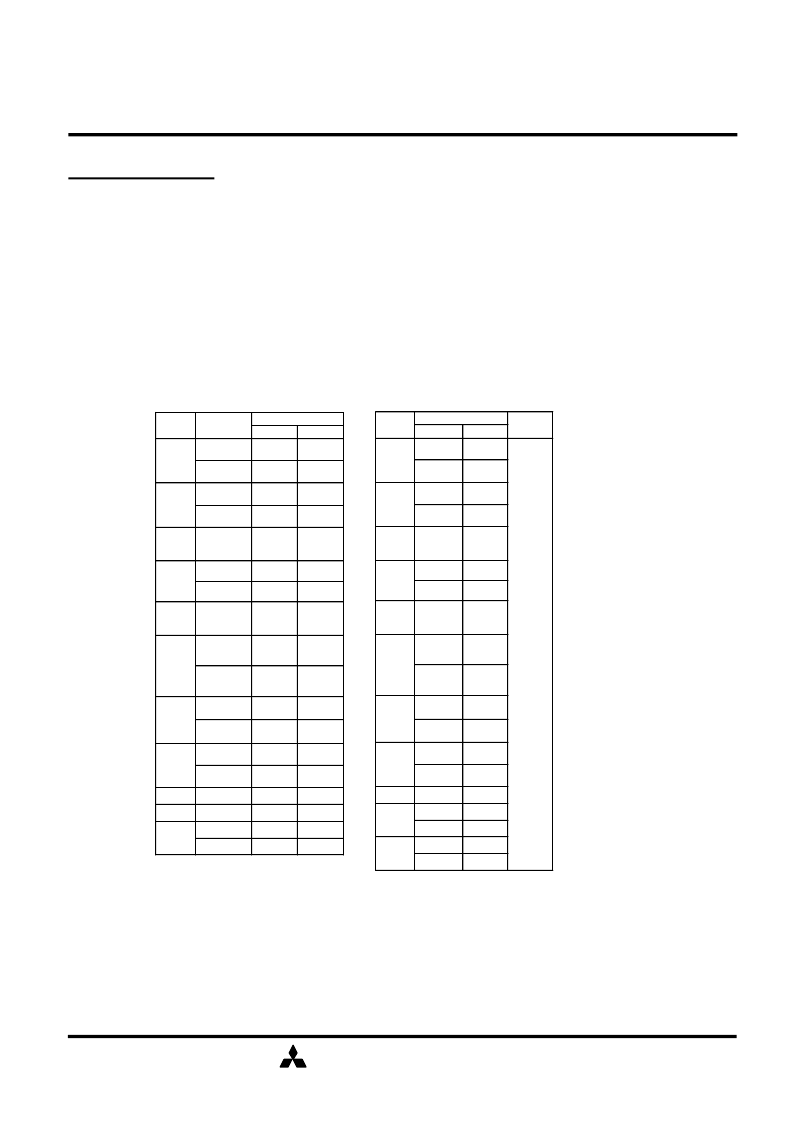

from

Limits(Max.)

-75

-10

x4

200

195

x8

205

200

x4

210

205

x8

215

210

x4

35

35

x8

40

40

x4

65

60

x8

70

65

x4

215

205

x8

225

215

x4

210

200

x8

220

210

IDD5

x4/x8

360

340

IDD6

x4/x8

6

6

x4

400

380

x8

410

390

x4/x8

IDD2P

IDD2F

IDD0

IDD1

Symbol

Organization

35

20

20

35

IDD7

IDD4W

x4/x8

IDD3P

IDD4R

IDD3N

to

-75

140

-10

130

140

130

150

140

160

150

30

25

30

15

25

12

45

35

45

35

190

140

220

170

180

150

210

180

IDD5

280

6

4

380

400

260

6

4

300

320

IDD6

-L

6

IDD4R

IDD3N

IDD2P

IDD2F

IDD0

IDD1

Symbol

mA

Unit

Limits(Max.)

IDD7

IDD4W

IDD3P

6

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M2V12D30TP-10L | 128 x 64 pixel format, LED Backlight available |

| M2V12D20TP | 512M Double Data Rate Synchronous DRAM |

| M2V12D20TP-75L | 512M Double Data Rate Synchronous DRAM |

| M2V12D30TP | 512M Double Data Rate Synchronous DRAM |

| M2V12D30TP-75L | 512M Double Data Rate Synchronous DRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M2S12D30TP-75 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:512M Double Data Rate Synchronous DRAM |

| M2S12D30TP-75L | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:512M Double Data Rate Synchronous DRAM |

| M2S150-1FC1152I | 制造商:Microsemi Corporation 功能描述:SMARTFUSION2 SOC FPGA - Trays |

| M2S150-1FCG1152 | 制造商:Microsemi Corporation 功能描述:SMARTFUSION2 SOC FPGA - Trays 制造商:Microsemi Corporation 功能描述:IC FPGA SOC 150K LUTS 1152FCBGA |

| M2S150-1FCG1152I | 制造商:Microsemi Corporation 功能描述:SMARTFUSION2 SOC FPGA - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。