- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄299424 > M2061-13I644.5313 (INTEGRATED DEVICE TECHNOLOGY INC) ATM/SONET/SDH SUPPORT CIRCUIT, CQCC36 PDF資料下載

參數(shù)資料

| 型號: | M2061-13I644.5313 |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | ATM/SONET/SDH SUPPORT CIRCUIT, CQCC36 |

| 封裝: | 9 X 9 MM, CERAMIC, LCC-36 |

| 文件頁數(shù): | 1/12頁 |

| 文件大?。?/td> | 477K |

| 代理商: | M2061-13I644.5313 |

M2060/61/62 M2065/66/67 Datasheet Rev 0.4

Revised 30Jul2004

Integr a t ed Cir cui t S ystems , Inc .

M2060/61/62

M2065/66/67

VCSO FEC PLL FOR SONET/OTN

Prelimina r y Inf o r m ation

GENERAL DESCRIPTION

The M2060/61/62 and M2065/66/67 are VCSO (Voltage

Controlled SAW Oscillator) based

clock PLLs designed for FEC clock

ratio translation in 10Gb optical

systems such as OC-192 or 10GbE.

They support FEC (Forward Error

Correction) clock multiplication

ratios, both forward (mapping) and

inverse (de-mapping). Multiplication ratios are

pin-selected from pre-programming look-up tables.

FEATURES

◆ Integrated SAW delay line; Output of 15 to 700 MHz *

◆ Low phase jitter < 0.5 ps rms typical

(12kHz to 20MHz or 50kHz to 80MHz)

◆ Pin-selectable PLL divider ratios support FEC ratios

M2060/65: OTU1 (255/238) and OTU2 (255/237) Mapping

M2061/66: OTU1 (238/255) or OTU2 (237/255) De-mapping

M2062/67: OTU1 (238/255) and OTU2 (237/255) De-mapping

◆ LVPECL clock output (CML and LVDS options available)

◆ Reference clock inputs support differential LVDS,

LVPECL, as well as single-ended LVCMOS, LVTTL

◆ Loss of Lock (LOL) output pin

◆ Narrow Bandwidth control input (NBW pin) to adjust

loop bandwidth

◆ Hitless Switching (HS) options with or without Phase

Build-out (PBO) available to enable SONET (GR-253)

/SDH (G.813) MTIE and TDEV compliance during

reference clock reselection

◆ Single 3.3V power supply

◆ Small 9 x 9 mm SMT (surface mount) package

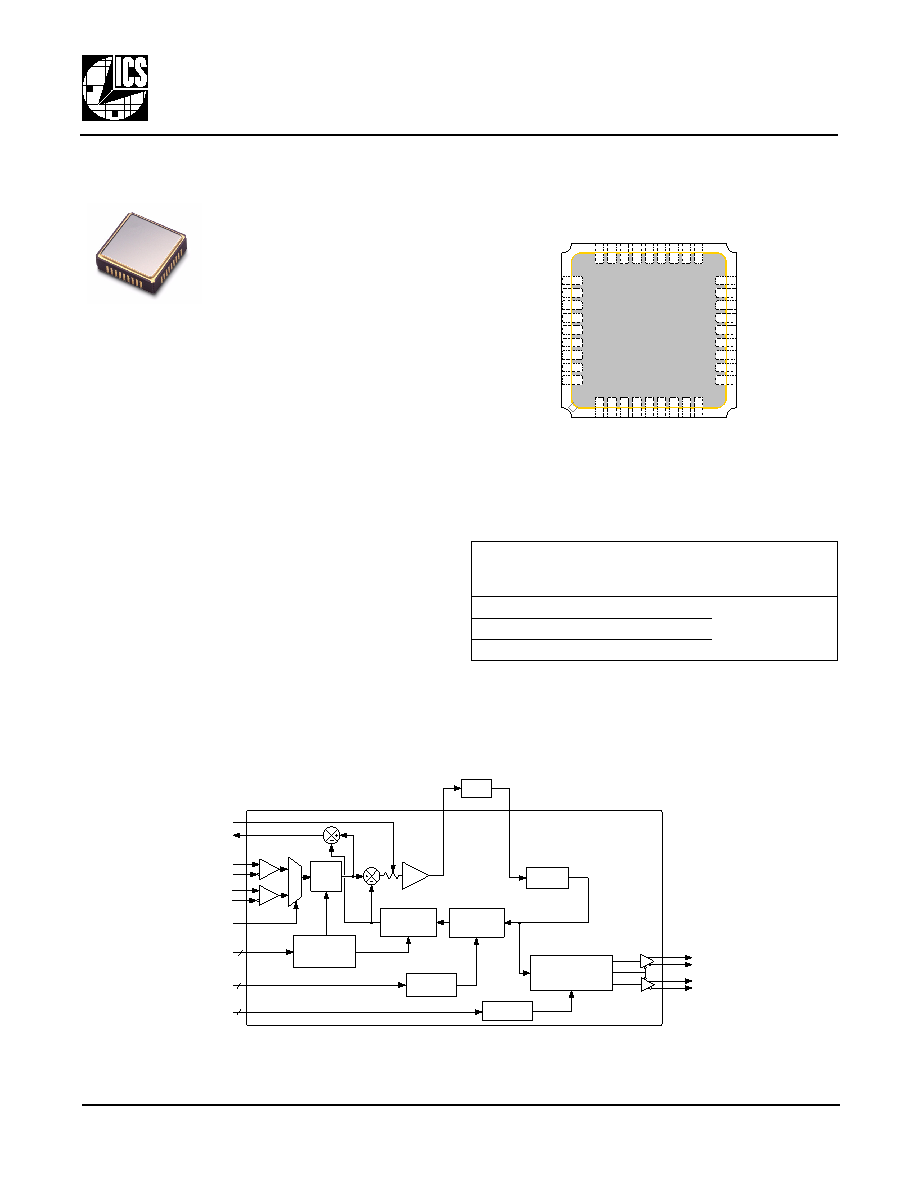

PIN ASSIGNMENT (9 x 9 mm SMT)

Figure 1: Pin Assignment

* Specify VCSO center frequency at time of order.

SIMPLIFIED BLOCK DIAGRAM

Figure 2: Simplified Block Diagram

Example I/O Clock Frequency Combinations

Using M2061-11-622.0800 FEC De-Map Ratios

FEC De-Map

PLL Ratio

Mfec / Rfec

Base Input Rate 1

(MHz)

Note 1: Input reference clock can be the base frequency shown

Output Clock

(either output)

MHz

1/1

622.0800

622.08

or

155.52

237/255

666.5143

238/255

669.3266

FIN_SEL1:0

P_SEL2:0

Loop

Filter

FEC_SEL1:0

M2060/61/62 VCSO FEC PLL for SONET/OTN

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M2061-13I666.5143LF | ATM/SONET/SDH SUPPORT CIRCUIT, CQCC36 |

| M2061-13I666.5143 | ATM/SONET/SDH SUPPORT CIRCUIT, CQCC36 |

| M2061-13I669.1281LF | ATM/SONET/SDH SUPPORT CIRCUIT, CQCC36 |

| M2061-13I669.1281 | ATM/SONET/SDH SUPPORT CIRCUIT, CQCC36 |

| M2061-13I669.3120LF | ATM/SONET/SDH SUPPORT CIRCUIT, CQCC36 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M20-6150405 | 制造商:HARWIN 制造商全稱:Harwin Plc 功能描述:PC104 PRESS-FIT CONNECTOR & SPACER (STACK THROUGH) |

| M20-6152005 | 功能描述:PC / 104 連接器 20P STACKTHROUGH PRESS FIT GOLD RoHS:否 制造商:Harwin 產(chǎn)品類型:Stackthrough 位置/觸點數(shù)量:64 端接類型:Press Fit 外殼材料:Polyphenylene Sulfide (PPS) 觸點材料:Phosphor Bronze 觸點電鍍:Gold |

| M20-6153205 | 功能描述:PC / 104 連接器 32P STACKTHROUGH PRESS FIT GOLD RoHS:否 制造商:Harwin 產(chǎn)品類型:Stackthrough 位置/觸點數(shù)量:64 端接類型:Press Fit 外殼材料:Polyphenylene Sulfide (PPS) 觸點材料:Phosphor Bronze 觸點電鍍:Gold |

| M20-6162005 | 功能描述:PC / 104 連接器 20P NON-STACKTHROUGH PRESS FIT GOLD RoHS:否 制造商:Harwin 產(chǎn)品類型:Stackthrough 位置/觸點數(shù)量:64 端接類型:Press Fit 外殼材料:Polyphenylene Sulfide (PPS) 觸點材料:Phosphor Bronze 觸點電鍍:Gold |

| M20-6163205 | 功能描述:PC / 104 連接器 32P NON-STACKTHROUGH PRESS FIT GOLD RoHS:否 制造商:Harwin 產(chǎn)品類型:Stackthrough 位置/觸點數(shù)量:64 端接類型:Press Fit 外殼材料:Polyphenylene Sulfide (PPS) 觸點材料:Phosphor Bronze 觸點電鍍:Gold |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。