- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄44968 > LSM2-T/16-D12G-C (CD TECHNOLOGIES INC) 1-OUTPUT 52.8 W DC-DC REG PWR SUPPLY MODULE PDF資料下載

參數(shù)資料

| 型號: | LSM2-T/16-D12G-C |

| 廠商: | CD TECHNOLOGIES INC |

| 元件分類: | 電源模塊 |

| 英文描述: | 1-OUTPUT 52.8 W DC-DC REG PWR SUPPLY MODULE |

| 封裝: | ROHS COMPLIANT PACKAGE-8 |

| 文件頁數(shù): | 5/17頁 |

| 文件大小: | 1504K |

| 代理商: | LSM2-T/16-D12G-C |

MDC_LSM2 Series.B01 Page 13 of 17

Technical enquiries email: sales@murata-ps.com, tel: +1 508 339 3000

www.murata-ps.com

LSM2 Series

Single Putput, Non-Isolated

Selectable-Output POL DC/DC Converters

Power Phasing Architectures

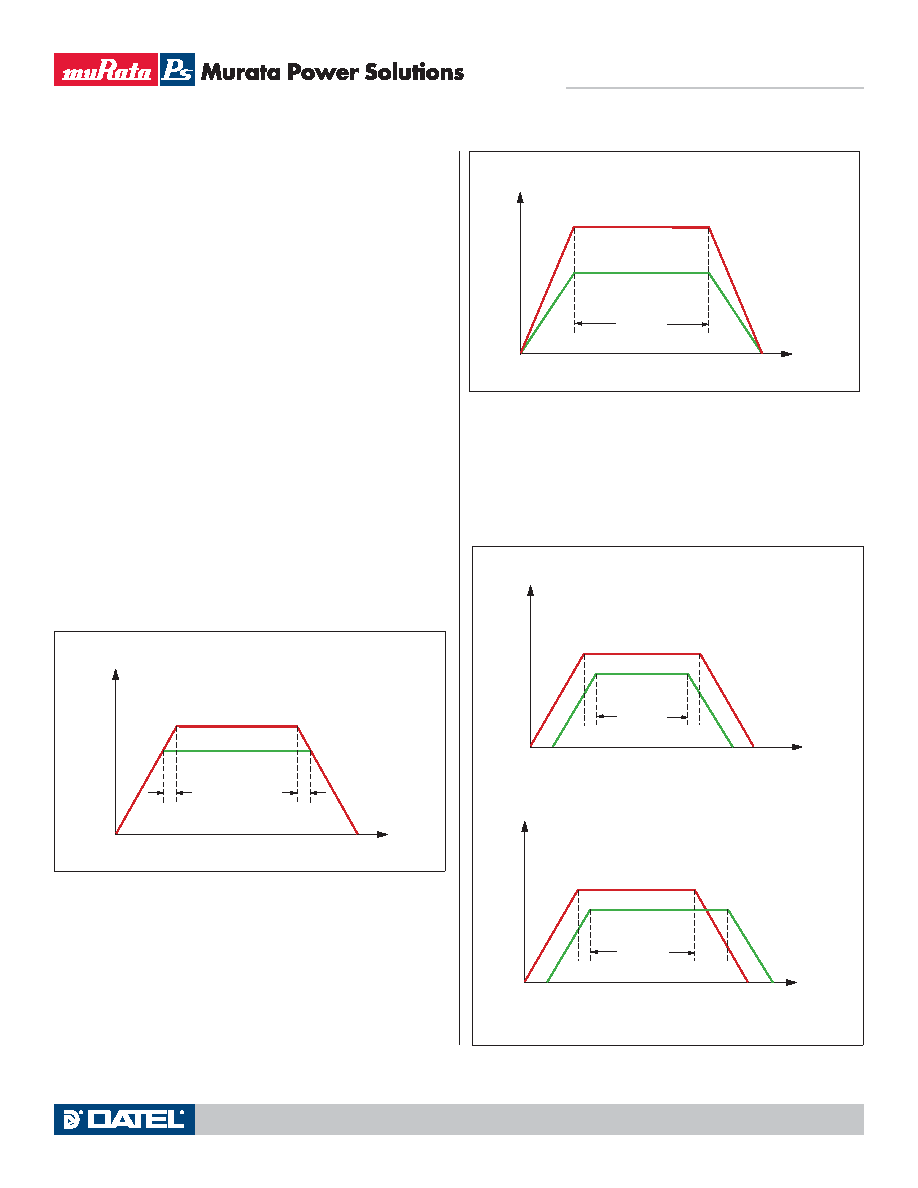

Observe the simplified timing diagrams below. There are many possible power

phasing architectures and these are just some examples to help you analyze

your system. Each application will be different. Multiple output voltages may

require more complex timing than that shown here.

These diagrams illustrate the time and slew rate relationship between two

typical power output voltages. Generally the Master will be a primary power

voltage in the system which must be present first or coincident with any

Slave power voltages. The Master output voltage is connected to the Slave’s

Sequence input, either by a voltage divider, divider-plus-capacitor or some

other method. Several standard sequencing architectures are prevalent. They

are concerned with three factors:

n

The time relationship between the Master and Slave voltages

n

The voltage difference relationship between the Master and Slave

n

The voltage slew rate (ramp slope) of each converter’s output.

For most systems, the time relationship is the dominant factor. The voltage

difference relationship is important for systems very concerned about possible

latchup of programmable devices or overdriving ESD diodes. Lower slew rates

avoid overcurrent shutdown during bypass cap charge-up.

In Figure 10, two POL’s ramp up at the same rate until they reach their

different respective final set point voltages. During the ramp, their voltages

are nearly identical. This avoids problems with large currents flowing between

logic systems which are not initialized yet. Since both end voltages are differ-

ent, each converter reaches it’s setpoint voltage at a different time.

Figures 12 and 13 show both delayed start up and delayed final voltages

for two converters. Figure 12 is called “Inclusive” because the later starting

POL finishes inside the earlier POL. The timing in Figure 12 is more easily built

using a combined digital sequence controller and the Sequence/Track pin.

Figure 13 is the same strategy as Figure 12 but with an “exclusive” timing

relationship staggered approximately the same at power-up and power-down.

Figure 11. Proportional or Ratiometric Phasing (Identical VOUT Time)

Figure 10. Coincident or Simultaneous Phasing (Identical Slew Rates)

Figure 12. Staggered or Sequential Phasing—Inclusive (Fixed Delays)

Figure 13. Staggered or Sequential Phasing—Exclusive

(Fixed Cascaded Delays)

Figure 11 shows two POL’s with different slew rates in order to reach differ-

ing final voltages at about the same time.

相關PDF資料 |

PDF描述 |

|---|---|

| LSM303DLHTR | SPECIALTY ANALOG CIRCUIT, PBGA28 |

| LSM330DL | SPECIALTY ANALOG CIRCUIT, PBGA28 |

| LSN-0.75/16-D12HJ-C | 1-OUTPUT 12.8 W DC-DC REG PWR SUPPLY MODULE |

| LSN-1.8/16-D12HJ-C | 1-OUTPUT 28.8 W DC-DC REG PWR SUPPLY MODULE |

| LSN-1.2/16-D12HJ-C | 1-OUTPUT 19.2 W DC-DC REG PWR SUPPLY MODULE |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| LSM2-T30-D12 | 制造商:MURATA 制造商全稱:Murata Manufacturing Co., Ltd. 功能描述:DOSA-SMT, 30A POL DC/DC Converters |

| LSM2-T-30-D12-C | 制造商:MURATA 制造商全稱:Murata Manufacturing Co., Ltd. 功能描述:DOSA-SMT, 30A POL DC/DC Converters |

| LSM2-T30-D12-C | 制造商:MURATA 制造商全稱:Murata Manufacturing Co., Ltd. 功能描述:DOSA-SMT, 30A POL DC/DC Converters |

| LSM2-T-30-D12R-C | 制造商:MURATA 制造商全稱:Murata Manufacturing Co., Ltd. 功能描述:DOSA-SMT, 30A POL DC/DC Converters |

| LSM2-T30-D12R-C | 制造商:MURATA 制造商全稱:Murata Manufacturing Co., Ltd. 功能描述:DOSA-SMT, 30A POL DC/DC Converters |

發(fā)布緊急采購,3分鐘左右您將得到回復。