- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369837 > LS7233-S Analog Miscellaneous PDF資料下載

參數(shù)資料

| 型號(hào): | LS7233-S |

| 英文描述: | Analog Miscellaneous |

| 中文描述: | 模擬雜項(xiàng) |

| 文件頁(yè)數(shù): | 5/8頁(yè) |

| 文件大?。?/td> | 73K |

| 代理商: | LS7233-S |

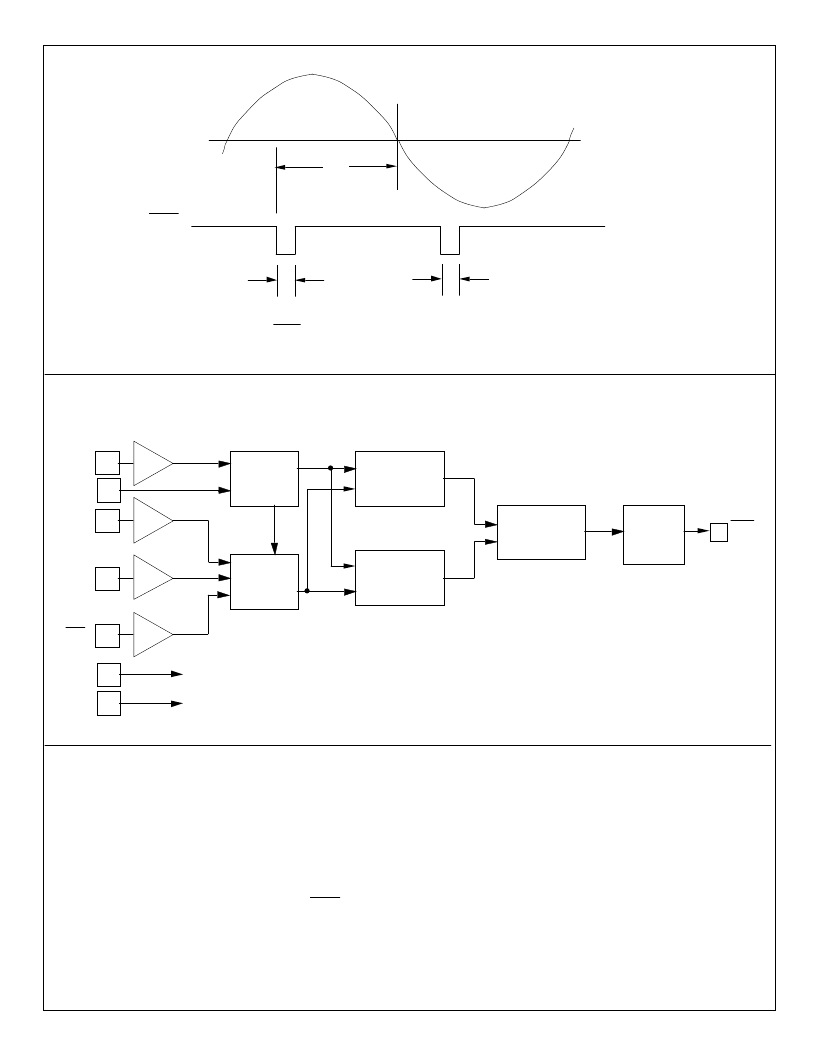

OUTPUT

DRIVER

DIGITAL

COMPARATOR

MEMORY

POINTER

PHASE

LOCK

LOOP

CONTROL

LOGIC

BUF

BUF

BUF

BUF

SYNC

CAP

DOZE

EXT

SENS

V

SS

V

DD

FIGURE 4

LS7231-4 BLOCK DIAGRAM

4

3

2

6

5

1

7

TRIG

(+V)

(-V)

8

APPLICATION EXAMPLE:

A typical implementation of a lamp dimmer circuit is shown in Fig. 5. Here the brightness of the lamp is set by touch-

ing the Touch Plate . The functions of different components are as follows:

The 15V DC supply for the chip is provided by Z, D1, R1, C2 and C5.

R2 and C4 generate the filtered signal for the SYNC input for synchronizing the internal PLL with the line

frequency.

R3 and C7 act as a filter circuit for the electronic extension. If extensions are not used, the EXT input (Pin 6)

should be tied to V

DD

(Pin 7).

R4, R5, R6 set up the sensitivity of the SENS input. C6 provides noise filtering.

C3 is the filter capacitor for the internal PLL.

R8 provides current limiting and isolation between the chip output and the triac gate.

C1 and L are RF filter circuits.

In the case of momentary power failure, the circuit state remains unchanged for a period of up to 1 sec. For longer

power interruptions, the output is shut off.

TRIG

SYNC

T

W

T

W

FIGURE 3. TRIG OUTPUT CONDUCTION ANGLE,

7231-4 040695-5

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LS7234-S | Analog Miscellaneous |

| LS7235 | Analog IC |

| LS7240 | Identity Comparator |

| LS7260C | Industrial Control IC |

| LS7260-S | Industrial Control IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LS7234 | 制造商:LSI 制造商全稱:LSI 功能描述:TOUCH CONTROL LAMP DIMMER |

| LS7234-S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog Miscellaneous |

| LS7235 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| LS7237 | 制造商:LSI 制造商全稱:LSI 功能描述:TOUCH CONTROL LAMP STEP DIMMER |

| LS7240 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Identity Comparator |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。