- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384602 > LM9820CCWM (NATIONAL SEMICONDUCTOR CORP) LM9810/20 10/12-Bit Image Sensor Processor Analog Front End PDF資料下載

參數(shù)資料

| 型號: | LM9820CCWM |

| 廠商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分類: | 模擬信號調(diào)理 |

| 英文描述: | LM9810/20 10/12-Bit Image Sensor Processor Analog Front End |

| 中文描述: | SPECIALTY ANALOG CIRCUIT, PDSO20 |

| 封裝: | PLASTIC, SOIC-20 |

| 文件頁數(shù): | 19/21頁 |

| 文件大小: | 148K |

| 代理商: | LM9820CCWM |

19

http://www.national.com

nation of the applied

SampCLK

and

MCLK

signals.

MCLK

is used to

synchronize the applied

SampCLK

signal. The internal ADC clock

will go low after the falling edge of

SampCLK

is clocked by a rising

of

MCLK

. The ADC clock will stay low for two

MCLK

cycles and

then go high. It will stay high until the next falling edge of

SampCLK

is clocked by

MCLK

. Figure 6 illustrates this

SampCLK

,

MCLK

, and

ADC clock timing relationship.

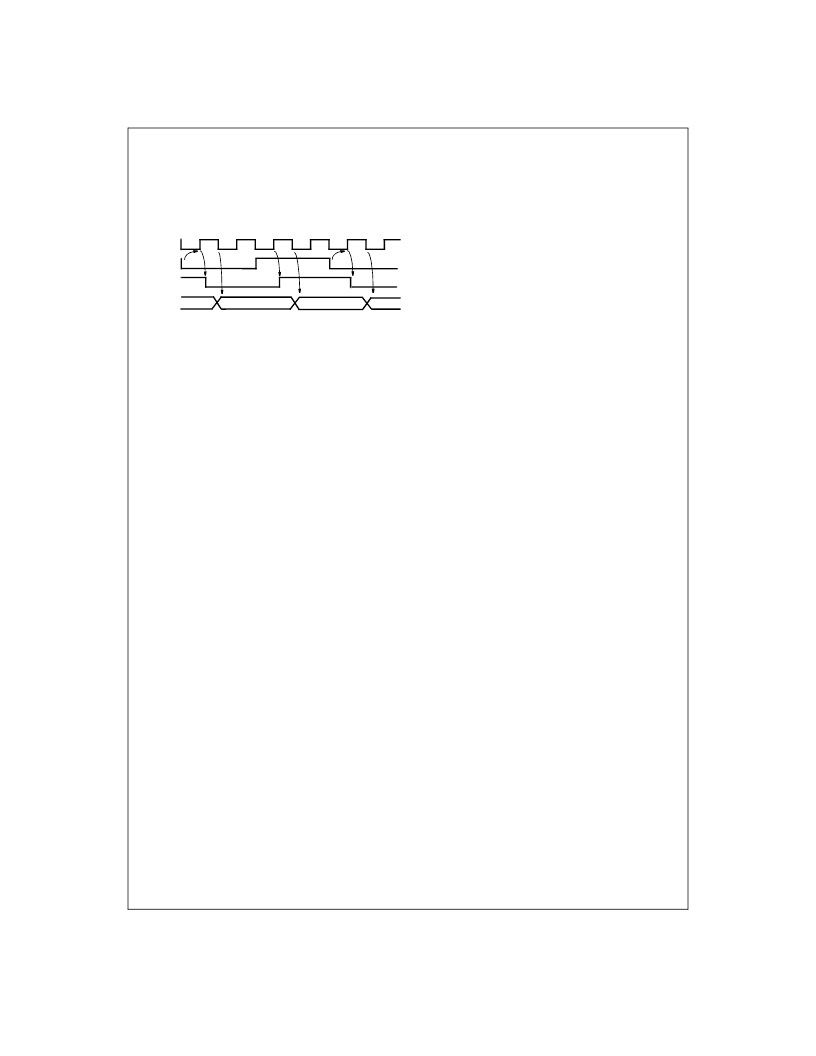

Figure 6: LM9810/20 Relative Event Timing

The LM9810/20 is a densely designed, mixed-signal, monolithic

semiconductor. In creating the timing for the LM9810/20, it must

be considered that internal events, such as ADC sampling, and

output data bus switching can potentially affect coincident events

such as input signal sampling or offset DAC settling. One event

can interfere with another by coupling noise on shared resources

such as the supply lines, internal voltage references, or the silicon

substrate.

To optimize the performance of the LM9810/20,

SampCLK

should

be timed so that the input signal hold times do not coincide with

output data switching and ADC clock transitions. In other words,

the rising and falling edges of

SampCLK

should not be placed

close to ADC clock edges or to output data transitions.

SampCLK

edges should be at least 20ns away from ADC clock edges to

avoid interference between the ADC and the sampler.

SampCLK

edges should also be placed at least 40ns after output data tran-

sition times to avoid transition noise coupling.

Figure 6 is an example of

SampCLK

timing that will meet these

requirements at the maximum

MCLK

frequency of 24MHz. In dia-

gram 6,

SampCLK

transitions occur on

MCLK

falling edges which

will keep them more than 20ns away from ADC transitions, and

40ns after output data transitions.

MCLK

SampCLK

ADC Clock

(internal)

D5 - D0

b11 - b6

b5 - b0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LM9810CCWMX | LM9810/20 10/12-Bit Image Sensor Processor Analog Front End |

| LM9820CCWMX | LM9810/20 10/12-Bit Image Sensor Processor Analog Front End |

| LM9812 | LM9812 30-Bit Color Linear CCD Sensor Processor |

| LM9812CCV | LM9812 30-Bit Color Linear CCD Sensor Processor |

| LM9823CCWM | LM9823 3 Channel 48-Bit Color Scanner Analog Front End |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LM9820CCWMX | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:LM9810/20 10/12-Bit Image Sensor Processor Analog Front End |

| LM9822 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:LM9822 3 Channel 42-Bit Color Scanner Analog Front End |

| LM9822CCWM | 制造商:Rochester Electronics LLC 功能描述: 制造商:Texas Instruments 功能描述: |

| LM9822CCWM/NOPB | 功能描述:ADC / DAC多通道 RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換速率: 分辨率:8 bit 接口類型:SPI 電壓參考: 電源電壓-最大:3.6 V 電源電壓-最小:2 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-40 |

| LM9822CCWM1 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:LM9822 3 Channel 42-Bit Color Scanner Analog Front End |

發(fā)布緊急采購,3分鐘左右您將得到回復。