- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄10129 > KSZ8041FTL TR (Micrel Inc)TXRX PHY 10/100 SGL LP 48TQFP PDF資料下載

參數(shù)資料

| 型號(hào): | KSZ8041FTL TR |

| 廠商: | Micrel Inc |

| 文件頁(yè)數(shù): | 19/58頁(yè) |

| 文件大小: | 0K |

| 描述: | TXRX PHY 10/100 SGL LP 48TQFP |

| 標(biāo)準(zhǔn)包裝: | 1,000 |

| 類型: | 收發(fā)器 |

| 驅(qū)動(dòng)器/接收器數(shù): | 1/1 |

| 規(guī)程: | SMII |

| 電源電壓: | 3.135 V ~ 3.465 V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 48-TQFP |

| 供應(yīng)商設(shè)備封裝: | 48-TQFP(7x7) |

| 包裝: | 帶卷 (TR) |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)當(dāng)前第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)

Micrel, Inc.

KSZ8041TL/FTL

April 2007

26

M9999-042707-1.1

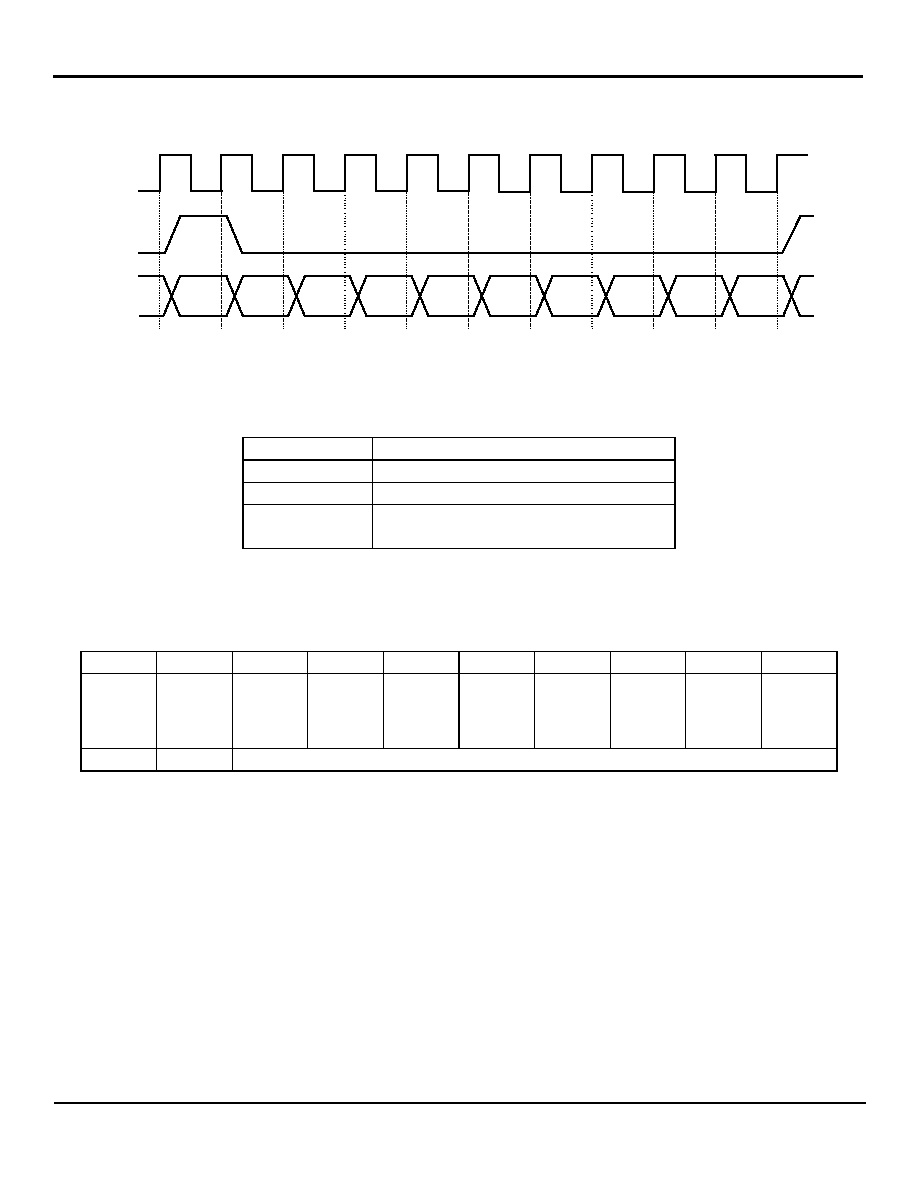

The following figure and table shows the receive data/control format for each segment:

CRS

RX_DV

RXD0

RXD1

RXD2

RXD3

RXD4

RXD5

RXD6

RXD7

CLOCK

SYNC

RX

Figure 3. SMII Receive Data/Control Segment

SMII RX Bit

Description

CRS

Carrier Sense

RX_DV

Receive Data Valid

RXD[0:7]

Encoded Data

See SMII RXD[0:7] Encoding Table (below)

Table 7. SMII RX Bit Description

CRS

RX_DV

RXD0

RXD1

RXD2

RXD3

RXD4

RXD5

RXD6

RXD7

X

0

RX_ER

from

pervious

frame

Speed

0=10M

1=100M

Duplex

0=Half

1=Full

Link

0=Down

1=Up

Jabber

0=No

1=Yes

Upper

Nibble

0=Invalid

1=Valid

False

Carrier

Detected

1

X

1

One Data Byte

Table 8. SMII RXD[0:7] Encoding Table

Collision Detection

Collisions occur when CRS and TX_EN are simultaneously asserted. The MAC regenerates the MII collision signal from

CRS and TX_EN.

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。