- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384544 > ISPLSI8600V-125LB272 (LATTICE SEMICONDUCTOR CORP) 3.3V In-System Programmable SuperBIG⑩ High Density PLD PDF資料下載

參數(shù)資料

| 型號: | ISPLSI8600V-125LB272 |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類: | PLD |

| 英文描述: | 3.3V In-System Programmable SuperBIG⑩ High Density PLD |

| 中文描述: | EE PLD, 13.5 ns, PBGA272 |

| 封裝: | BGA-272 |

| 文件頁數(shù): | 16/26頁 |

| 文件大小: | 333K |

| 代理商: | ISPLSI8600V-125LB272 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當(dāng)前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁

Specifications

ispLSI 8600V

16

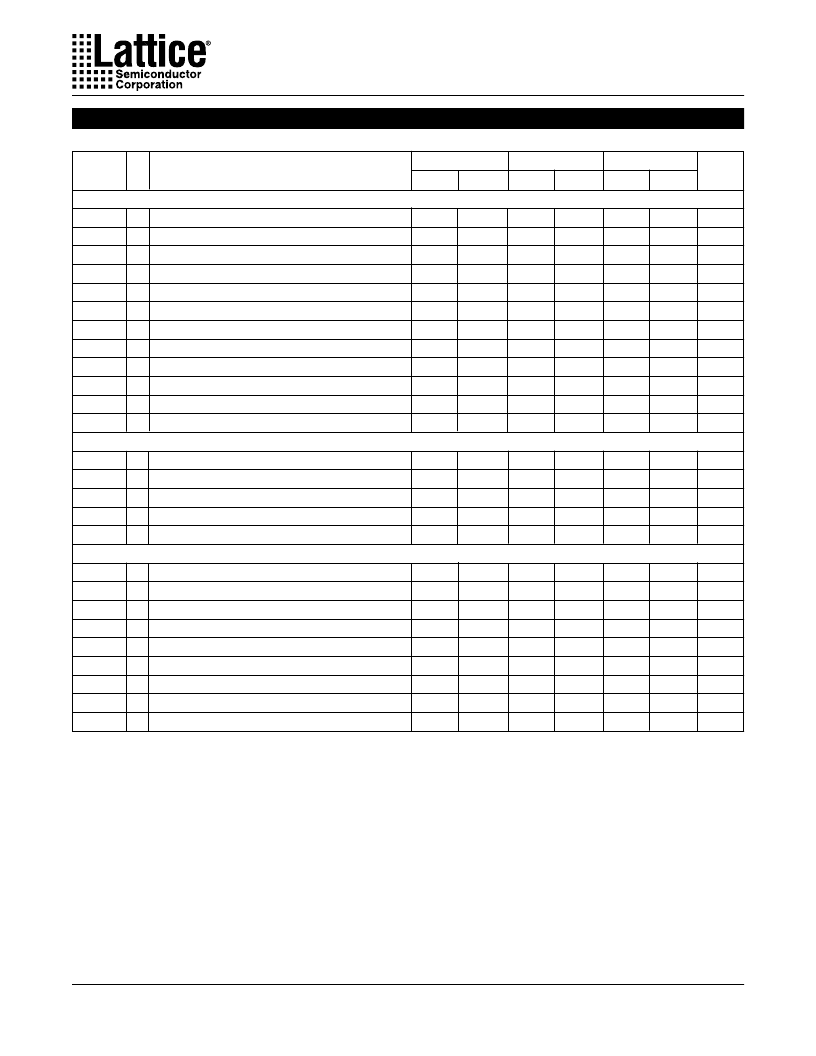

Internal Timing Parameters

Over Recommended Operating Conditions

BFM / Global Routing Pool Delay

t

bfmi

61 BFM Routing Delay, Signal from I/O Cell

t

grpi

62 GRP Delay, Signal from I/O Cell

t

grpiz

63 Internal Tristate Bus Enable/Disable, I/O Cell Buffer

t

bfmm

64 BFM Routing Delay, Signal from Macrocell

t

grpm

65 GRP Delay, Signal from Macrocell

t

grpmz

66

Internal Tristate Bus Enable/Disable, Macrocell Buffer

t

bfmg

67 BFM Routing Delay, Signal from GRP

t

grpb

68 GRP Delay, Signal from BFM Routing

t

bcom

69 BFM Routing to I/O Cell, Combinatorial Path

t

breg

70 BFM Routing to I/O Cell, Registered Path

t

gcom

71 GRP to I/O Cell, Combinatorial Path

t

greg

72 GRP to I/O Cell, Registered Path

I/O Control Bus Delay

t

piock

73 Product Term as I/O Cell Register Clock

t

piocken 74 Product Term as I/O Cell Register Clock Enable

t

poe

75 Product Term as Output Buffer Enable/Disable

t

piorst

76

Product Term as I/O Cell Register Reset or Set Delay

t

pioz

77 Internal Tristate Bus Control Signal for I/O Cell Buffer

Global Control Delay

t

gck

78 Global Macrocell Register Clk

t

gcken

79 Global Macrocell Register Clk Enable

t

giock

80 Global I/O Register Clk

t

giocken 81 Global I/O Register Clk Enable

t

qck

82 Quadrant I/O Register Clk

t

goe

83 Global Output Enable

t

toe

84 Test Output Enable

t

gmrst

85 Global GLB Register Reset

t

giorst

86 Global I/O Cell Register Reset

1. Internal Timing Parameters are not tested and are for reference only.

2. Refer to Timing Model in this data sheet for further details.

0.4

–

–

–

–

–

–

–

–

–

–

–

1.0

1.6

4.1

0.6

2.0

3.0

2.5

1.3

1.5

2.3

0.8

1.6

0.6

–

–

–

–

–

–

–

–

–

–

–

1.3

1.9

4.9

0.7

3.0

4.3

3.3

1.5

1.7

2.6

0.8

1.7

0.8

–

–

–

–

–

–

–

–

–

–

–

1.9

2.8

7.3

1.1

4.5

6.5

4.9

2.3

2.6

4.0

1.2

2.6

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

–

–

–

–

–

4.1

4.6

5.6

4.3

3.3

–

–

–

–

–

4.7

5.3

6.5

5.0

3.8

–

–

–

–

–

7.2

8.1

9.9

7.6

5.8

ns

ns

ns

ns

ns

3.9

6.4

3.4

6.5

1.9

–

–

–

–

4.1

6.4

3.9

6.5

1.9

5.6

8.5

7.6

5.4

4.3

7.5

4.0

7.5

2.0

–

–

–

–

4.9

7.5

4.4

7.5

2.9

8.3

10.1

7.8

6.4

6.6

11.4

6.1

11.4

3.1

–

–

–

–

7.5

11.4

6.5

11.4

4.5

12.4

15.2

11.8

9.6

ns

ns

ns

ns

ns

ns

ns

ns

ns

-125

-90

-60

MIN

MAX

MIN

MAX

MIN

MAX

UNITS

PARA-

METER #

2

DESCRIPTION

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ISPLSI8600V-125LB492 | 3.3V In-System Programmable SuperBIG⑩ High Density PLD |

| ISPLSI8600V-60LB272 | 3.3V In-System Programmable SuperBIG⑩ High Density PLD |

| ISPLSI8600V-60LB492 | 3.3V In-System Programmable SuperBIG⑩ High Density PLD |

| ISPLSI8600V-90LB272 | GT 14C 14#16 SKT RECP LINE |

| ISPLSI8600V-90LB492 | GT 14C 14#16 SKT RECP LINE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ISPLSI8600V-125LB492 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| ispLSI8600V-60LB272 | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 USE ispMACH 5000MV RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| ISPLSI-8600V-60LB272I | 制造商:Rochester Electronics LLC 功能描述: 制造商:Lattice Semiconductor Corporation 功能描述: |

| ISPLSI8600V-60LB492 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| ispLSI8600V-90LB272 | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 USE ispMACH 5000MV RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。