- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384544 > ISPLSI81080V-90LB272 (LATTICE SEMICONDUCTOR CORP) 3.3V In-System Programmable SuperBIG⑩ High Density PLD PDF資料下載

參數(shù)資料

| 型號: | ISPLSI81080V-90LB272 |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類: | PLD |

| 英文描述: | 3.3V In-System Programmable SuperBIG⑩ High Density PLD |

| 中文描述: | EE PLD, 16 ns, PBGA272 |

| 封裝: | THERMALLY ENHANCED, BGA-272 |

| 文件頁數(shù): | 14/26頁 |

| 文件大小: | 333K |

| 代理商: | ISPLSI81080V-90LB272 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁

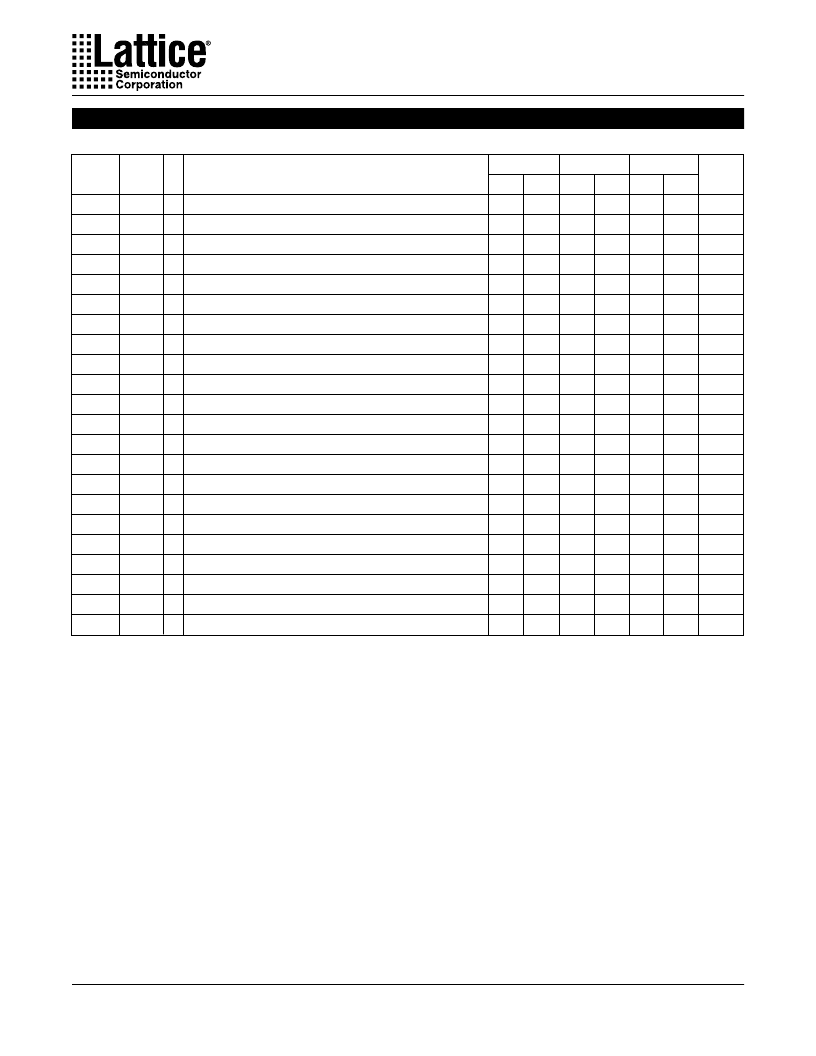

Specifications

ispLSI 81080V

14

t

pd1

t

pd2

f

max

UNITS

-90

-60

MIN.

—

—

TEST

COND.

Table 2-0030/81080V

MAX.

15.0

24.0

DESCRIPTION

#

PARA-

METER

A

A

1 Prop Delay, BFM Input to Same BFM Output, 4 PT Bypass

2 Prop Delay, Global Input to Global Output

3 Clk Frequency, Local Feedback, Same GLB

—

—

10.0

16.0

ns

ns

t

suq

t

hq

t

coq

t

sug

t

hg

t

cog

t

su1

t

h1

t

co1

t

suceq

t

hceq

t

suceg

t

hceg

t

goe

t

rglb

t

rio

t

rw

t

wh

t

wl

1. Unless noted otherwise, all parameters use PTSA and CLK0.

2. Refer to Timing Model in this data sheet for further details.

3. Standard 20-bit counter with local feedback.

4. Refer to Switching Test Conditions section.

—

4 I/O Cell Reg, Data Setup Time, Quadrant I/O Clock

5 I/O Cell Reg, Data Hold Time, Quadrant I/O Clock

6 I/O Cell Reg, Quadrant Clock to Output Delay

7 I/O Cell Reg, Data Setup Time, Global Clock

8 I/O Cell Reg, Data Hold Time, Global Clock

9 I/O Cell Reg, Global Clock to Output Delay

10 GLB Reg Setup, BFM Input to Same BFM GLB, 4 PT Bypass

11 GLB Reg Hold Time, BFM Input to Same BFM GLB

12 GLB Reg, Global Clock to Same BFM Output Delay

13 I/O Cell Reg, CLKEN Setup Time, Quadrant I/O Clock

14 I/O Cell Reg, CLKEN Hold Time, Quadrant I/O Clock

15 GLB Reg, CLKEN Setup Time, Global Clock

16 GLB Reg, CLKEN Hold Time, Global Clock

17 Global Output Enable/Disable Delay

18 Global Reset/Preset Time, GLB Reg

19 Global Reset/Preset Time, I/O Cell Reg

20 Global Reset/Preset Pulse Duration

21 Global or Quadrant Clock Pulse, High Duration

22 Global or Quadrant Clock Pulse, Low Duration

8.0

—

ns

—

A

—

—

A

—

6.0

—

—

7.5

ns

ns

ns

ns

ns

—

—

—

—

ns

ns

0.0

A

—

—

—

—

B/C

10.0

—

—

—

—

10.0

ns

ns

ns

ns

ns

ns

6.5

0.0

4.5

0.0

—

—

—

—

—

—

6.5

15.0

10.0

—

ns

ns

ns

0.0

—

6.0

0.0

—

7.0

—

14.5

—

—

6.0

—

ns

—

6.0

—

ns

—

90.0

—

12.0

—

—

9.0

—

—

11.0

—

—

0.0

15.0

—

—

—

—

15.0

9.5

0.0

6.5

0.0

—

—

—

9.5

22.0

15.0

—

0.0

—

9.0

0.0

—

10.0

—

9.0

—

9.0

—

60.0

—

MHz

-125

MIN. MAX.

MIN. MAX.

—

—

8.5

5.0

—

4.0

—

—

6.0

—

—

0.0

8.0

—

—

—

—

7.0

5.5

0.0

3.5

0.0

—

—

—

5.0

14.0

8.5

—

0.0

—

3.5

0.0

—

4.5

—

4.0

—

4.0

—

125.0

4

2

3

External Switching Characteristics

1

Over Recommended Operating Conditions

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ISPLSI81080V-125LB492 | 3.3V In-System Programmable SuperBIG⑩ High Density PLD |

| ISPLSI81080V-90LB492 | 3.3V In-System Programmable SuperBIG⑩ High Density PLD |

| ISPLSI8600V-125LB272 | 3.3V In-System Programmable SuperBIG⑩ High Density PLD |

| ISPLSI8600V-125LB492 | 3.3V In-System Programmable SuperBIG⑩ High Density PLD |

| ISPLSI8600V-60LB272 | 3.3V In-System Programmable SuperBIG⑩ High Density PLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ISPLSI81080V-90LB492 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| ISPLSI-8600V-125LB272 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Lattice Semiconductor Corporation 功能描述: |

| ispLSI8600V-125LB272 | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 USE ispMACH 5000MV RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| ISPLSI8600V-125LB492 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| ispLSI8600V-60LB272 | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 USE ispMACH 5000MV RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。