- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384543 > ISPLSI5128VE (Lattice Semiconductor Corporation) In-System Programmable 3.3V SuperWIDE High Density PLD PDF資料下載

參數(shù)資料

| 型號: | ISPLSI5128VE |

| 廠商: | Lattice Semiconductor Corporation |

| 英文描述: | In-System Programmable 3.3V SuperWIDE High Density PLD |

| 中文描述: | 在系統(tǒng)可編程3.3超寬高密度可編程邏輯器件 |

| 文件頁數(shù): | 18/21頁 |

| 文件大?。?/td> | 211K |

| 代理商: | ISPLSI5128VE |

Specifications

ispLSI 5128VE

18

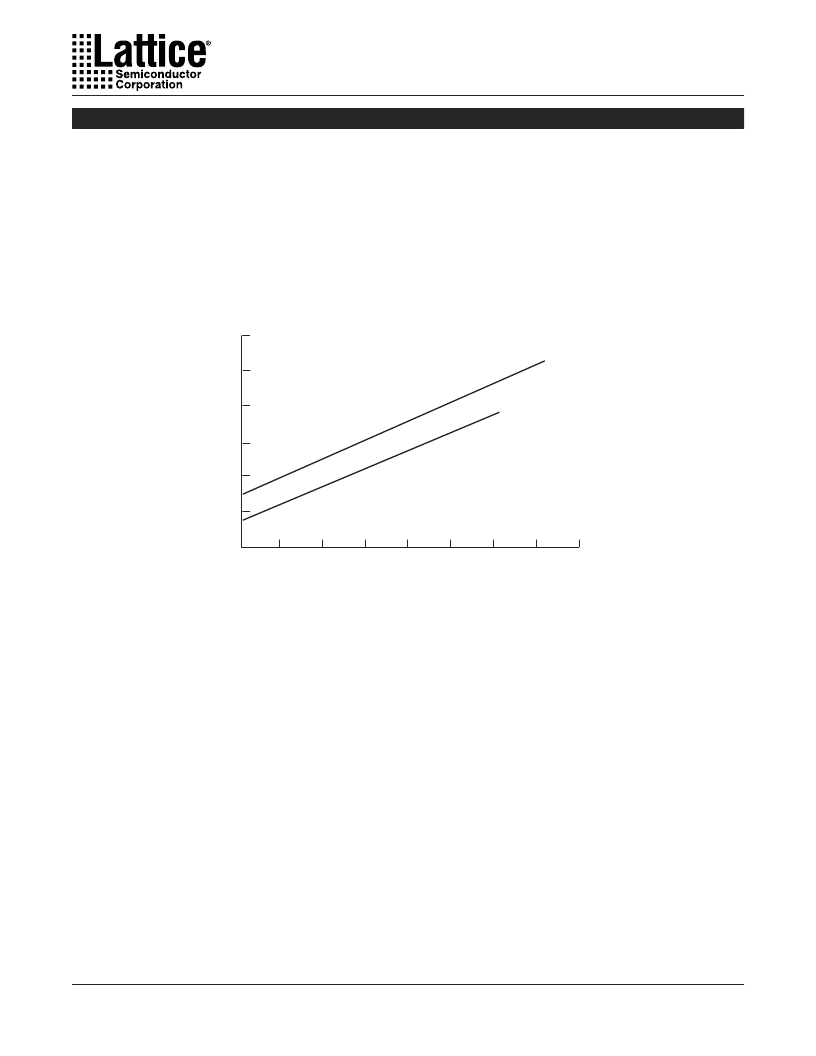

Power Consumption

setting operates product terms at their normal full power

consumption. For portions of the logic that can tolerate

longer propagation delays, selecting the slower “l(fā)ow-

power” setting will reduce the power dissipation for these

product terms. Figure 10 shows the relationship between

power and operating frequency.

Power consumption in the ispLSI 5128VE device de-

pends on two primary factors: the speed at which the

device is operating and the number of product terms

used. The product terms have a fuse-selectable speed/

power tradeoff setting. Each group of five product terms

has a single speed/power tradeoff control fuse that acts

on the complete group of five. The fast “high-speed”

105

0

25

50

75

100

125

150

175

200

f

max (MHz)

I

C

Notes: Configuration of 8 16-bit Counters

Typical Current at 3.3V, 25

°

C

ispLSI 5128VE

High Speed Mode

ispLSI 5128VE

Low Power Mode

0127/5128VE

ICC can be estimated for the ispLSI 5128VE using the following equation:

High Speed Mode:

ICC = 12.4 + (# of PTs * 0.408) + (# of nets * Fmax * 0.00169)

Low Power Mode:

ICC = 12.4 + (# of PTs * 0.349) + (# of nets * Fmax * 0.00169)

# of PTs = Number of Product Terms used in design

# of nets = Number of Signals used in device

Fmax = Highest Clock Frequency to the device

The ICC estimate is based on typical conditions (VCC = 3.3V, room temperature) and an assumption of one GLB load

on average exists. These values are for estimates only. Since the value of ICC is sensitive to operating conditions

and the program in the device, the actual ICC should be verified.

135

165

180

150

120

90

Figure 10. Typical Device Power Consumption vs fmax

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ISPLSI5128VE-80LT128I | In-System Programmable 3.3V SuperWIDE High Density PLD |

| ISPLSI5128VE-100LT128 | In-System Programmable 3.3V SuperWIDE High Density PLD |

| ISPLSI5128VE-100LT128I | In-System Programmable 3.3V SuperWIDE High Density PLD |

| ISPLSI5128VE-125LT128 | In-System Programmable 3.3V SuperWIDE High Density PLD |

| ISPLSI5128VE-125LT128I | In-System Programmable 3.3V SuperWIDE High Density PLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ISPLSI5128VE-100LT128 | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| ISPLSI5128VE-100LT128I | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| ISPLSI5128VE-125LT128 | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| ISPLSI5128VE-125LT128I | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| ISPLSI5128VE-180LT128 | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。