- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384543 > ISPLSI5128VE-180LT128 (LATTICE SEMICONDUCTOR CORP) In-System Programmable 3.3V SuperWIDE High Density PLD PDF資料下載

參數(shù)資料

| 型號: | ISPLSI5128VE-180LT128 |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類: | PLD |

| 英文描述: | In-System Programmable 3.3V SuperWIDE High Density PLD |

| 中文描述: | EE PLD, 5 ns, PQFP128 |

| 封裝: | TQFP-128 |

| 文件頁數(shù): | 8/21頁 |

| 文件大?。?/td> | 211K |

| 代理商: | ISPLSI5128VE-180LT128 |

Specifications

ispLSI 5128VE

8

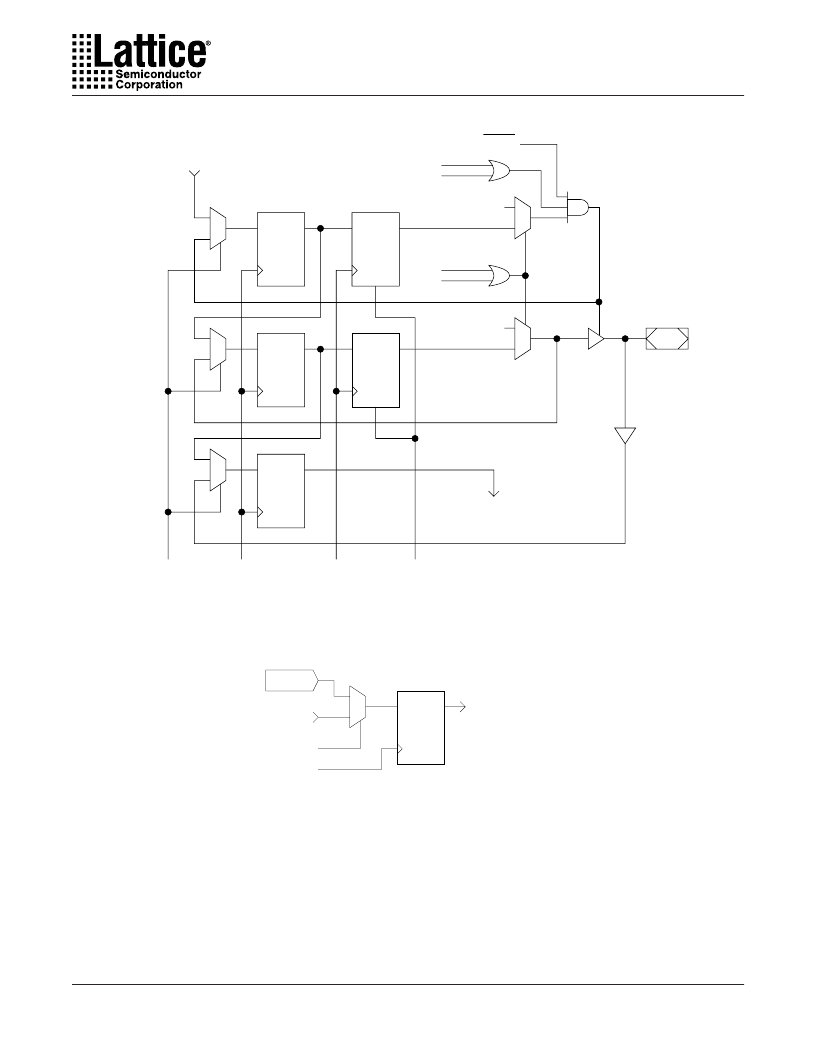

Figure 6. Boundary Scan Register Circuit for I/O Pins

Figure 7. Boundary Scan Register Circuit for Input-Only Pins

Normal

Function

OE

EXTEST

Update DR

SCANOUT

(to next cell)

Clock DR

SCANIN

(from previous

cell)

Shift DR

Normal

Function

TOE

D

Q

D

Q

D

Q

D

1

0

1

0

1

0

Q

D

Q

I/O Pin

Reset

BSCAN

Registers

BSCAN

Latches

HIGHZ

0

PROG_MODE

EXTEST

1

0

1

SCANOUT

(to next cell)

Clock DR

SCANIN

(from previous

cell)

Shift DR

D

Q

Input Pin

0

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ISPLSI5128VE-180LT128I | In-System Programmable 3.3V SuperWIDE High Density PLD |

| ISPLSI5128VE-80LT128 | In-System Programmable 3.3V SuperWIDE High Density PLD |

| ISPLSI5256VA-125LQ208 | In-System Programmable 3.3V SuperWIDE⑩ High Density PLD |

| ISPLSI5256VA-100LB208 | In-System Programmable 3.3V SuperWIDE⑩ High Density PLD |

| ISPLSI5256VA-100LB272 | In-System Programmable 3.3V SuperWIDE⑩ High Density PLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ISPLSI5128VE-180LTN128 | 制造商:Lattice Semiconductor 功能描述:CPLD ispLSI? 5000VE Family 6K Gates 128 Macro Cells 180MHz 3.3V 128-Pin TQFP |

| ISPLSI5128VE-80LT128I | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| ISPLSI5256VA-100LB208 | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| ISPLSI5256VA-100LB208I | 制造商:Lattice Semiconductor Corporation 功能描述:COMPLEX-EEPLD, 256-CELL, 13NS PROP DELAY, 208 Pin, Plastic, BGA |

| ISPLSI5256VA-100LB272 | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。