- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384510 > IRS21367 (International Rectifier) 3-PHASE BRIDGE DRIVER PDF資料下載

參數(shù)資料

| 型號(hào): | IRS21367 |

| 廠商: | International Rectifier |

| 英文描述: | 3-PHASE BRIDGE DRIVER |

| 中文描述: | 3相橋式驅(qū)動(dòng)器 |

| 文件頁(yè)數(shù): | 14/23頁(yè) |

| 文件大?。?/td> | 614K |

| 代理商: | IRS21367 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)

www.irf.com

14

IRS213(6,62,63,65,66,67,68) (J&S)PbF

1 PCB Layout Tips

1.1 Distance from H to L Voltage

The IRS2136xJ package lacks some pins (see page 11) in order to maximizing the distance between the high voltage

and low voltage pins. It’s strongly recommended to place the components tied to the floating voltage in the respective

high voltage portions of the device (V

B1,2,3

, V

S1,2,3

) side.

1.2 Ground Plane

To minimize noise coupling ground plane must not be placed under or near the high voltage floating side.

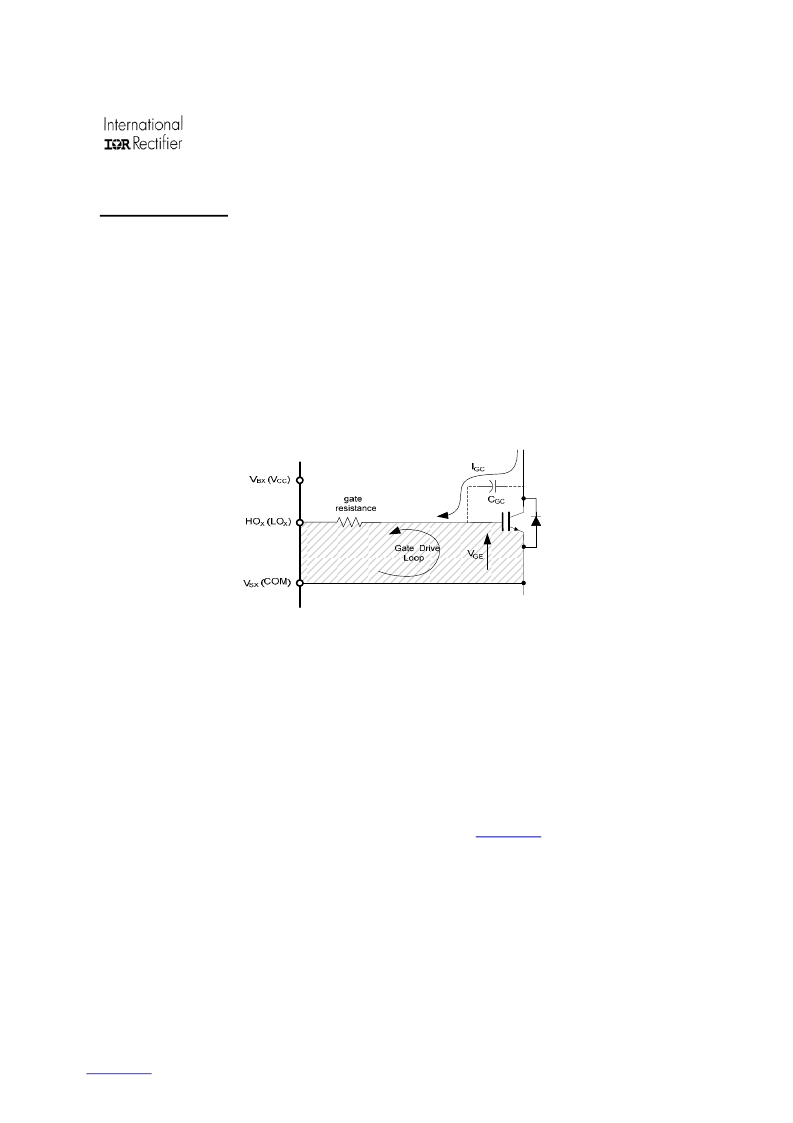

1.3 Gate Drive Loops

Current loops behave like an antenna able to receive and transmit EM noise (see Fig. 7). In order to reduce EM coupling

and improve the power switch turn on/off performances, gate drive loops must be reduced as much as possible.

Moreover, current can be injected inside the gate drive loop via the IGBT collector-to-gate parasitic capacitance. The

parasitic auto-inductance of the gate loop contributes to develop a voltage across the gate-emitter increasing the

possibility of self turn-on effect.

Fig. 7. Antenna Loops

1.4 Supply Capacitors

Supply capacitors must be placed as close as possible to the device pins (V

CC

and V

SS

for the ground tied supply, V

B

and

V

S

for the floating supply) in order to minimize parasitic inductance/resistance.

1.5 Routing and Placement

Power stage PCB parasitic may generate dangerous voltage transients for the gate driver and the control logic. In

particular it’s recommended to limit phase voltage negative transients.

In order to avoid such undervoltage it is highly recommended to minimize high side emitter to low side collector distance

and low side emitter to negative bus rail stray inductance. See DT04-4 at

www.irf.com

for more detailed information.

PRELIMINARY

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IRS21368JPbF | 3-PHASE BRIDGE DRIVER |

| IRS21368SPbF | 3-PHASE BRIDGE DRIVER |

| IRS2153D | SELF-OSCILLATING HALF-BRIDEGE DRIVER IC |

| IRS2153DPBF | SELF-OSCILLATING HALF-BRIDEGE DRIVER IC |

| IRS2153DSPBF | SELF-OSCILLATING HALF-BRIDEGE DRIVER IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IRS21367D | 制造商:IRF 制造商全稱:International Rectifier 功能描述:3-PHASE BRIDGE DRIVER |

| IRS21368DJPBF | 制造商:IRF 制造商全稱:International Rectifier 功能描述:3-PHASE BRIDGE DRIVER |

| IRS21368DSPBF | 制造商:IRF 制造商全稱:International Rectifier 功能描述:3-PHASE BRIDGE DRIVER |

| IRS21368JPBF | 制造商:IRF 制造商全稱:International Rectifier 功能描述:3-PHASE BRIDGE DRIVER |

| IRS21368SPBF | 制造商:IRF 制造商全稱:International Rectifier 功能描述:3-PHASE BRIDGE DRIVER |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。