- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄299227 > IRD-L67132L-70 (TEMIC SEMICONDUCTORS) 2K X 8 DUAL-PORT SRAM, 70 ns, PQFP64 PDF資料下載

參數(shù)資料

| 型號(hào): | IRD-L67132L-70 |

| 廠商: | TEMIC SEMICONDUCTORS |

| 元件分類: | SRAM |

| 英文描述: | 2K X 8 DUAL-PORT SRAM, 70 ns, PQFP64 |

| 封裝: | VQFP-64 |

| 文件頁(yè)數(shù): | 9/14頁(yè) |

| 文件大?。?/td> | 178K |

| 代理商: | IRD-L67132L-70 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)當(dāng)前第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)

L67132/L67142

Rev. D (19 Fev. 97)

4

MATRA MHS

Truth Table

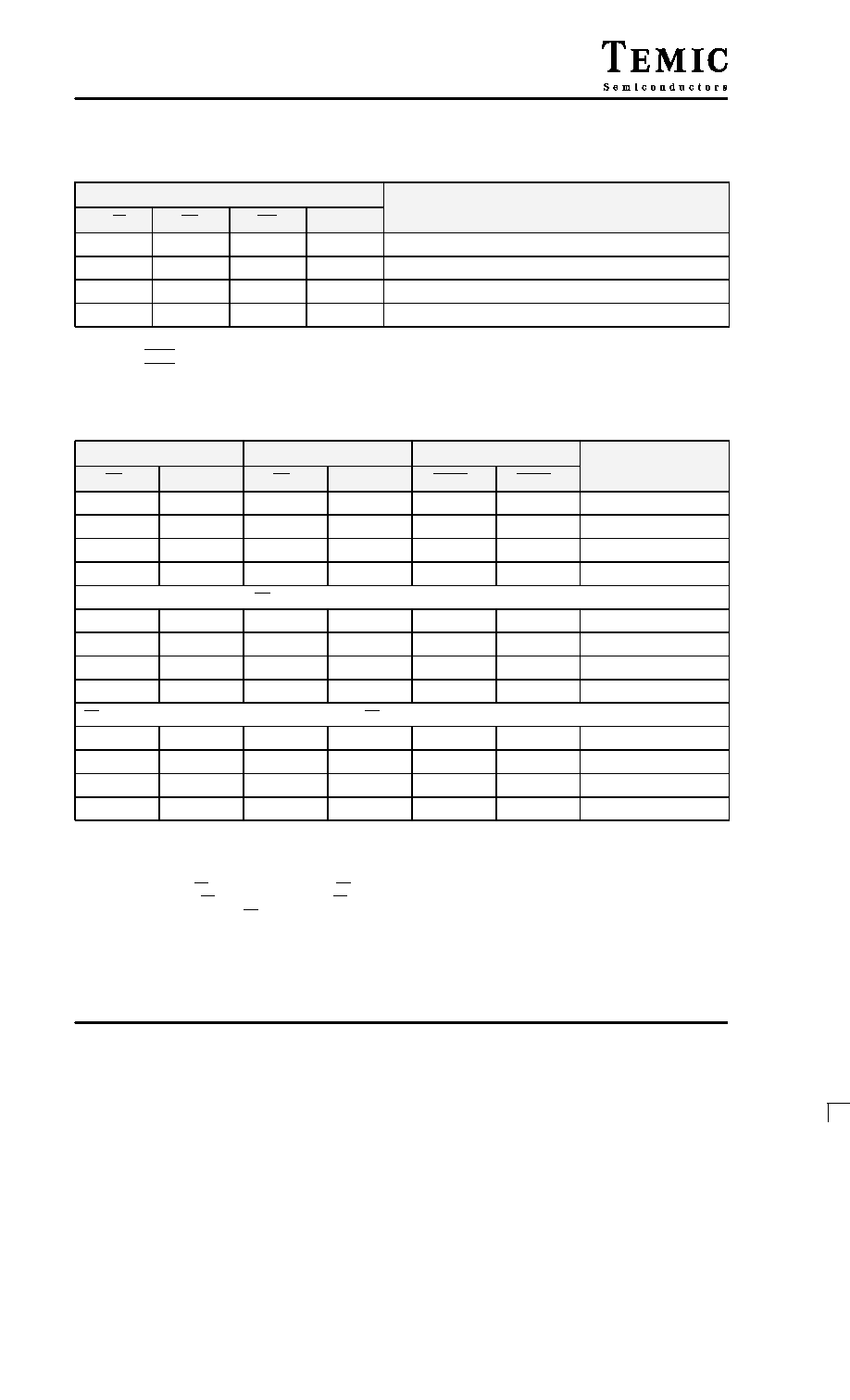

Table 1 : Non Contention Read/Write Control(4)

LEFT OR RIGHT PORT(1)

FUNCTION

R/W

CS

OE

D0–7

FUNCTION

X

H

X

Z

Port Disabled and in Power Down Mode. ICCSB or ICCSB1

L

X

DATAIN

Data on Port Written into memory(2)

H

L

DATAOUT

Data in Memory Output on Port(3)

H

L

H

Z

High Impedance Outputs

Notes :

1. AOL – A10L ≠ A0R – A10R.

2. If BUSY = L, data is not written.

3. If BUSY = L, data may not be valid, see tWDD and tDDD timing.

4. H = HIGH, L = LOW, X = DON’T CARE, Z = HIGH IMPEDANCE.

Table 2 : Arbitration(5)

LEFT PORT

RIGHT PORT

FLAGS

FUNCTION

CSL

A0L – A10L

CSR

A0L – A10R

BUSYL

BUSYR

FUNCTION

H

X

H

X

H

No Contention

L

Any

H

X

H

No Contention

H

X

L

Any

H

No Contention

L

≠ A0R – A10R

L

≠ A0L – A10L

H

No Contention

ADDRESS ARBITRATION WITH CE LOW BEFORE ADDRESS MATCH

L

LV5R

L

LV5R

H

L

L–Port Wins

L

RV5L

L

RV5L

L

H

R–Port Wins

L

Same

L

Same

H

L

Arbitration Resolved

L

Same

L

Same

L

H

Arbitration Resolved

CS ARBITRATION WITH ADDRESS MATCH BEFORE CS

LL5R

= A0R – A10R

LL5R

= A0L – A10L

H

L

L–Port Wins

RL5L

= A0R – A10R

RL5L

= A0L – A10L

L

H

R–Port Wins

LW5R

= A0R – A10R

LW5R

= A0L – A10L

H

L

Arbitration Resolved

LW5R

= A0R – A10R

LW5R

= A0L – A10L

L

H

Arbitration Resolved

Notes :

5. X = DON’T CARE, L = LOW, H = HIGH.

LV5R = Left Address Valid

≥ 5 ns before right address.

RV5L = Right address Valid

≥ 5 ns before left address.

Same = Left and Right Addresses match within 5 ns of each other.

LL5R = Left CS = LOW

≥ 5 ns before Right CS.

RL5L = Right CS = LOW

≥ 5 ns before left CS.

LW5R = Left and Right CS = LOW within 5 ns of each other.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| I4K-L67142V-55 | 2K X 8 DUAL-PORT SRAM, 55 ns, CQCC48 |

| M1K-L67142L-70/883 | 2K X 8 DUAL-PORT SRAM, 70 ns, CDIP48 |

| IS32WV10008ALL-85BI | 1M X 8 PSEUDO STATIC RAM, 85 ns, PBGA48 |

| IS42LS16800A | 16Meg x 8, 8Meg x16 & 4Meg x 32 128-MBIT SYNCHRONOUS DRAM |

| IS42LS16800A-10B | 16Meg x 8, 8Meg x16 & 4Meg x 32 128-MBIT SYNCHRONOUS DRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IRD-LPC1768-DEV | 功能描述:開(kāi)發(fā)板和工具包 - ARM Ind. Ref. Design LPC1768 Dev Kit V1 RoHS:否 制造商:Arduino 產(chǎn)品:Development Boards 工具用于評(píng)估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口類型:DAC, ICSP, JTAG, UART, USB 工作電源電壓:3.3 V |

| IRD-LPC2468-DEV | 功能描述:開(kāi)發(fā)板和工具包 - ARM Ind. Ref. Design LPC2468 Dev Kit V1.2 RoHS:否 制造商:Arduino 產(chǎn)品:Development Boards 工具用于評(píng)估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口類型:DAC, ICSP, JTAG, UART, USB 工作電源電壓:3.3 V |

| IRE-1.0 | 制造商:Speakercraft 功能描述:Standard IR Emitter |

| IRE-2.0 | 制造商:Speakercraft 功能描述:Standard Dual IR Emitter |

| IRE-3.0 | 制造商:Speakercraft 功能描述:Standard IR Emitter with Visible LED |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。