- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4583 > IDT72V51433L7-5BB (IDT, Integrated Device Technology Inc)IC FLOW CTRL MULTI QUEUE 256-BGA PDF資料下載

參數(shù)資料

| 型號: | IDT72V51433L7-5BB |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁數(shù): | 33/50頁 |

| 文件大小: | 0K |

| 描述: | IC FLOW CTRL MULTI QUEUE 256-BGA |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 類型: | 多隊列流量控制 |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 256-BBGA |

| 供應(yīng)商設(shè)備封裝: | 256-BGA(17x17) |

| 包裝: | 托盤 |

| 其它名稱: | 72V51433L7-5BB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁當(dāng)前第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁

39

IDT72V51433/72V51443/72V51453 3.3V, MULTI-QUEUE FLOW-CONTROL DEVICES

(16 QUEUES) 18 BIT WIDE CONFIGURATION 589,824, 1,179,648 and 2,359,296 bits

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

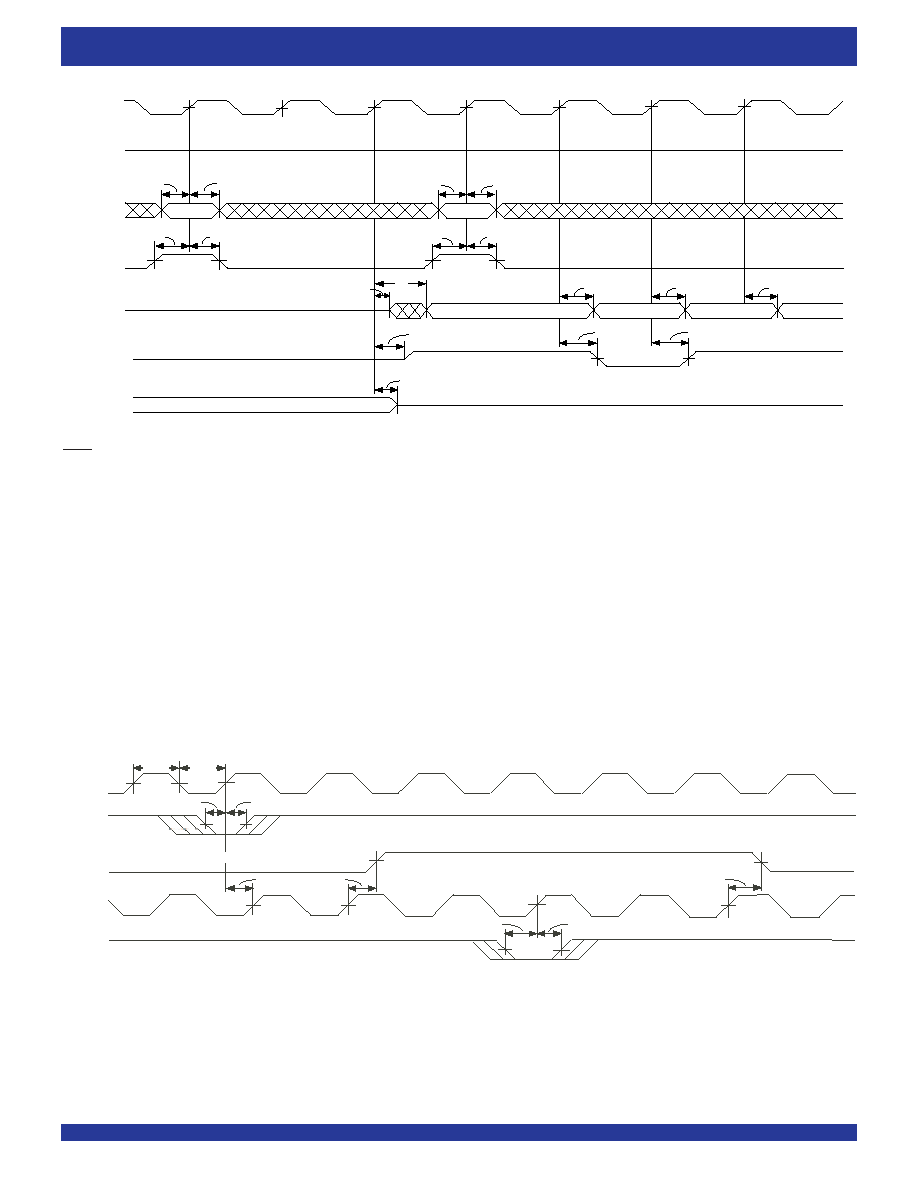

Figure 20. Almost Empty Flag Timing and Queue Switch

Figure 21. Almost Empty Flag Timing

RCLK

RADEN

tQH

tQS

tAH

tAS

RDADD

D1 Q12

PAE

(Device 1)

tAELZ

5939 drw22

REN

tAH

tAS

tQH

tQS

tOLZ

Qout

tRAE

HIGH-Z

D1 Q15

PAE

(Device 2)

tAEHZ

HIGH

HIGH-Z

tA

D1 Q12 Wn

HIGH-Z

*B*

*C*

*E*

*F*

*D*

*A*

tA

D1 Q12 Wn+1

tA

D1 Q15 W0

tA

D1 Q15 W1

*G*

WCLK

tENH

tCLKH

tCLKL

WEN

PAE

RCLK

tENS

n+1 words in Queue

tRAE

tSKEW2

tRAE

12

REN

5939 drw23

tENS

tENH

n+2 words in Queue

n+1 words in Queue

Cycle:

*A* Queue 12 of Device 1 is selected on the read port. A queue within Device 2 had previously been selected. The

PAE flag output and the data outputs of device 1 are High-Impedance.

*B* No read occurs.

*C* The

PAE flag output now switches to device 1. Word, Wn is read from Q12 due to the FWFT operation. This read operation from Q12 is at the almost empty boundary, therefore

PAE will go LOW 2 RCLK cycles later.

*D* Q15 of device 1 is selected.

*E* The

PAE flag goes LOW due to the read from Q12 2 RCLK cycles earlier. Word Wn+1 is read out due to the FWFT operation.

*F* Word, W0 is read from Q15 due to the FWFT operation. The

PAE flag goes HIGH to show that Q15 is not almost empty.

NOTE:

1. The waveform here shows the

PAE flag operation when no queue switches are occurring and a queue selected on both the write and read ports is being written to then read

from at the almost empty boundary.

Flag Latencies:

Assertion: 2*RCLK + tRAE

De-assertion: tSKEW2 + RCLK + tRAE

If tSKEW2 is violated there will be one extra RCLK cycle.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LFEC10E-4QN208I | IC FPGA 10.2KLUTS 208PQFP |

| MIC5320-SFYMT TR | IC REG LDO 3.3V/1.5V .15A 6-TMLF |

| MIC5310-PPYML TR | IC REG LDO 3V .15A 8-MLF |

| EB41-S0C5040X | CONN EDGEBOARD DUAL 100POS 3A |

| LFEC10E-5QN208C | IC FPGA 10.2KLUTS 147I/O 208QFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72V51433L7-5BB8 | 功能描述:IC FLOW CTRL MULTI QUEUE 256-BGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT72V51433L7-5BBI | 功能描述:IC FLOW CTRL MULTI QUEUE 256-BGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT72V51436L6BB | 功能描述:IC FLOW CTRL MULTI QUEUE 256-BGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT72V51436L6BB8 | 功能描述:IC FLOW CTRL MULTI QUEUE 256-BGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT72V51436L7-5BB | 功能描述:IC FLOW CTRL MULTI QUEUE 256-BGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。