- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄9966 > IDT723622L12PQF (IDT, Integrated Device Technology Inc)IC FIFO SYNC 256X36X2 132QFP PDF資料下載

參數(shù)資料

| 型號(hào): | IDT723622L12PQF |

| 廠(chǎng)商: | IDT, Integrated Device Technology Inc |

| 文件頁(yè)數(shù): | 3/25頁(yè) |

| 文件大小: | 0K |

| 描述: | IC FIFO SYNC 256X36X2 132QFP |

| 標(biāo)準(zhǔn)包裝: | 36 |

| 系列: | 7200 |

| 功能: | 同步 |

| 存儲(chǔ)容量: | 18.4K(256 x 36 x 2) |

| 數(shù)據(jù)速率: | 83MHz |

| 訪(fǎng)問(wèn)時(shí)間: | 12ns |

| 電源電壓: | 4.5 V ~ 5.5 V |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類(lèi)型: | 表面貼裝 |

| 封裝/外殼: | 132-BQFP 緩沖式 |

| 供應(yīng)商設(shè)備封裝: | 132-PQFP(24.13x24.13) |

| 包裝: | 托盤(pán) |

| 其它名稱(chēng): | 723622L12PQF |

第1頁(yè)第2頁(yè)當(dāng)前第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)

11

IDT723622/723632/723642 CMOS SyncBiFIFO

256 x 36 x 2, 512 x 36 x 2, 1,024 x 36 x 2

COMMERCIALTEMPERATURERANGE

The setup and hold time constraints to the port Clocks for the port Chip

Selects and Write/Read selects are only for enabling write and read

operations and are not related to high-impedance control of the data

outputs. If a port enable is LOW during a clock cycle, the port’s Chip Select

and Write/Read select may change states during the setup and hold time

window of the cycle.

When a FIFO Output Ready flag is LOW, the next word written is

automaticallysenttotheFIFOoutputregisterautomaticallybytheLOW-to-HIGH

transitionoftheportclockthatsetstheOutputReadyflagHIGH. WhentheOutput

ReadyflagisHIGH,subsequentdataisclockedtotheoutputregistersonlywhen

aFIFOreadisselectedusingtheport’sChipSelect,Write/Readselect,Enable,

and Mailbox select.

SYNCHRONIZED FIFO FLAGS

Each FIFO is synchronized to its port clock through at least two flip-flop

stages. This is done to improve flag-signal reliability by reducing the

probability of metastable events when CLKA and CLKB operate asynchro-

nously to one another. ORA,

AEA, IRA, and AFA are synchronized to CLKA.

ORB,

AEB, IRB, and AFB are synchronized to CLKB. Tables 4 and 5 show

the relationship of each port flag to FIFO1 and FIFO2.

OUTPUT READY FLAGS (ORA, ORB)

The Output Ready flag of a FIFO is synchronized to the port clock that

reads data from its array. When the Output Ready flag is HIGH, new data

is present in the FIFO output register. When the Output Ready flag is LOW,

thepreviousdatawordispresentintheFIFOoutputregisterandattemptedFIFO

reads are ignored.

A FIFO read pointer is incremented each time a new word is clocked to

itsoutputregister.ThestatemachinethatcontrolsanOutputReadyflagmonitors

a write pointer and read pointer comparator that indicates when the FIFO

memory status is empty, empty+1, or empty+2. From the time a word is written

toaFIFO,itcanbeshiftedtotheFIFOoutputregisterinaminimumofthreecycles

of the Output Ready flagsynchronizing clock. Therefore, an Output Readyflag

isLOWifawordinmemoryisthenextdatatobesenttotheFlFOoutputregister

andthreecyclesoftheportClockthatreadsdatafromtheFIFOhavenotelapsed

sincethetimethewordwaswritten.TheOutputReadyflagoftheFIFOremains

LOW until the third LOW-to-HIGH transition of the synchronizing clock occurs,

simultaneouslyforcingtheOutputReadyflagHIGHandshiftingthewordtothe

FIFO output register.

A LOW-to-HIGH transition on an Output Ready flag synchronizing clock

begins the first synchronization cycle of a write if the clock transition occurs at

timetSKEW1orgreaterafterthewrite.Otherwise,thesubsequentclockcyclecan

bethefirstsynchronizationcycle(seeFigures8and9forORAandORBtiming

diagrams).

INPUT READY FLAGS (IRA, IRB)

TheInputReadyflagofaFlFOissynchronizedtotheportclockthatwrites

data to its array. When the Input Ready flag is HIGH, a memory location is free

in the FIFO to receive new data. No memory locations are free when the Input

Ready flag is LOW and attempted writes to the FIFO are ignored.

Each time a word is written to a FIFO, its write pointer is incremented. The

statemachinethatcontrolsanInputReadyflagmonitorsawritepointerandread

pointercomparatorthatindicateswhentheFlFOmemorystatusisfull,full-1,or

CSB

W/RB

ENB

MBB

CLKB

Data B (B0-B35) I/O

PORT FUNCTION

H

X

High-Impedance

None

L

X

Input

None

LL

H

L

↑

Input

FIFO2 write

LL

H

↑

Input

Mail2 write

L

H

L

X

Output

None

LH

H

L

↑

Output

FIFO1 read

L

H

L

H

X

Output

None

LH

H

↑

Output

Mail1 read (set

MBF1 HIGH)

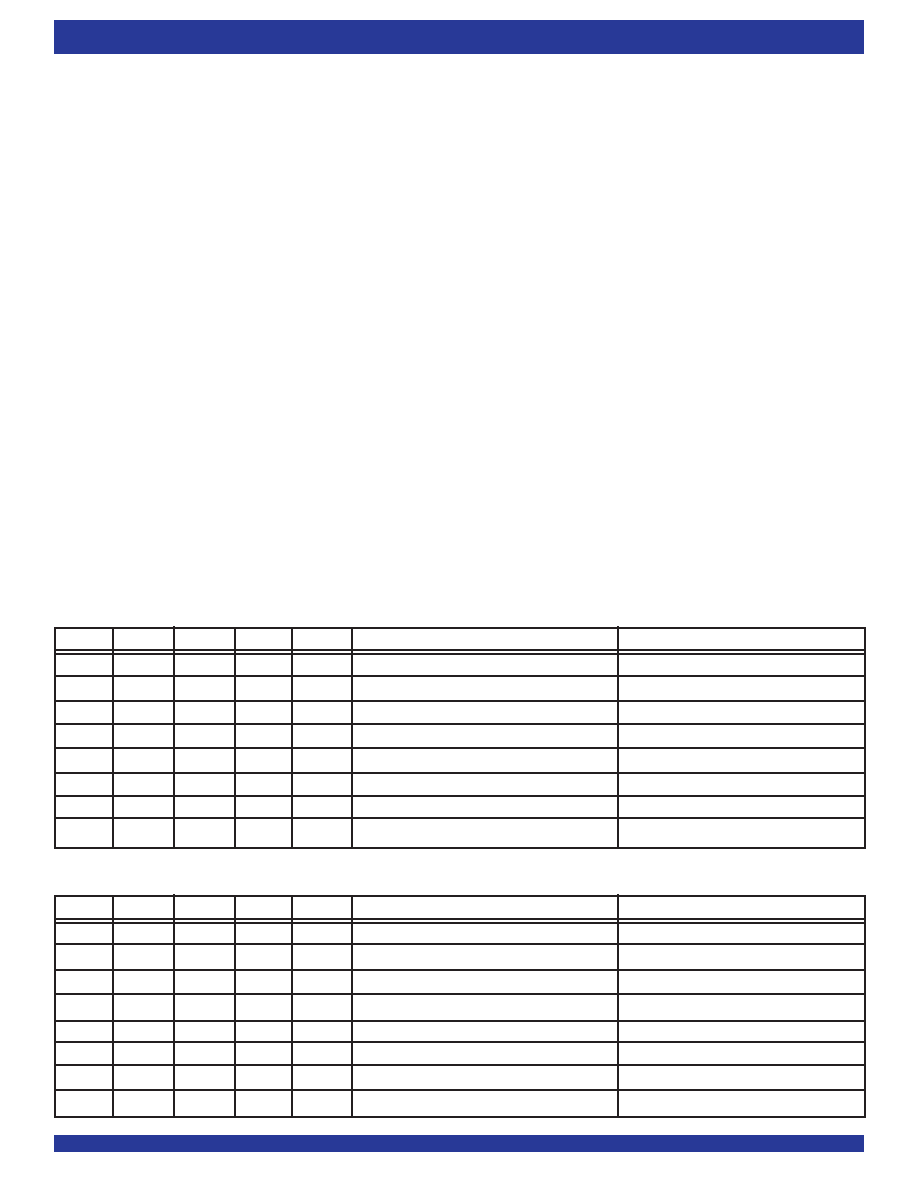

TABLE 3 — PORT B ENABLE FUNCTION TABLE

TABLE 2 — PORT A ENABLE FUNCTION TABLE

CSA

W/

RA

ENA

MBA

CLKA

Data A (A0-A35) I/O

PORT FUNCTION

H

X

High-Impedance

None

L

H

L

X

Input

None

LH

H

L

↑

Input

FIFO1 write

LH

H

↑

Input

Mail1 write

L

X

Output

None

LL

H

L

↑

Output

FIFO2 read

L

H

X

Output

None

LL

H

↑

Output

Mail2 read (set

MBF2 HIGH)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MS27466E13A35SC | CONN RCPT 22POS WALL MNT W/SCKT |

| D38999/24FA98SD | CONN RCPT 3POS JAM NUT W/SCKT |

| MAX1109CUB+ | IC ADC 8BIT LP 10-UMAX |

| MS27508E16B26SA | CONN RCPT 26POS BOX MNT W/SCKT |

| MS27656E15F18PA | CONN RCPT 18POS WALL MNT W/PINS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT723622L15PF | 功能描述:IC FIFO SYNC 256X36X2 120QFP RoHS:否 類(lèi)別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪(fǎng)問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤(pán) 其它名稱(chēng):72271LA10PF |

| IDT723622L15PF8 | 功能描述:IC FIFO SYNC 256X36X2 120QFP RoHS:否 類(lèi)別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪(fǎng)問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤(pán) 其它名稱(chēng):72271LA10PF |

| IDT723622L15PQF | 功能描述:IC FIFO SYNC 256X36X2 132QFP RoHS:否 類(lèi)別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪(fǎng)問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤(pán) 其它名稱(chēng):72271LA10PF |

| IDT723623L12PF | 功能描述:IC FIFO SYNC 1KX9 12NS 128QFP RoHS:否 類(lèi)別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪(fǎng)問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤(pán) 其它名稱(chēng):72271LA10PF |

| IDT723623L12PF8 | 功能描述:IC FIFO SYNC 1KX9 12NS 128QFP RoHS:否 類(lèi)別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪(fǎng)問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤(pán) 其它名稱(chēng):72271LA10PF |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。