- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384480 > ID82C82 (HARRIS SEMICONDUCTOR) CMOS Octal Latching Bus Driver PDF資料下載

參數(shù)資料

| 型號: | ID82C82 |

| 廠商: | HARRIS SEMICONDUCTOR |

| 元件分類: | 通用總線功能 |

| 英文描述: | CMOS Octal Latching Bus Driver |

| 中文描述: | CMOS SERIES, 8-BIT DRIVER, TRUE OUTPUT, CDIP20 |

| 文件頁數(shù): | 2/7頁 |

| 文件大小: | 103K |

| 代理商: | ID82C82 |

4-275

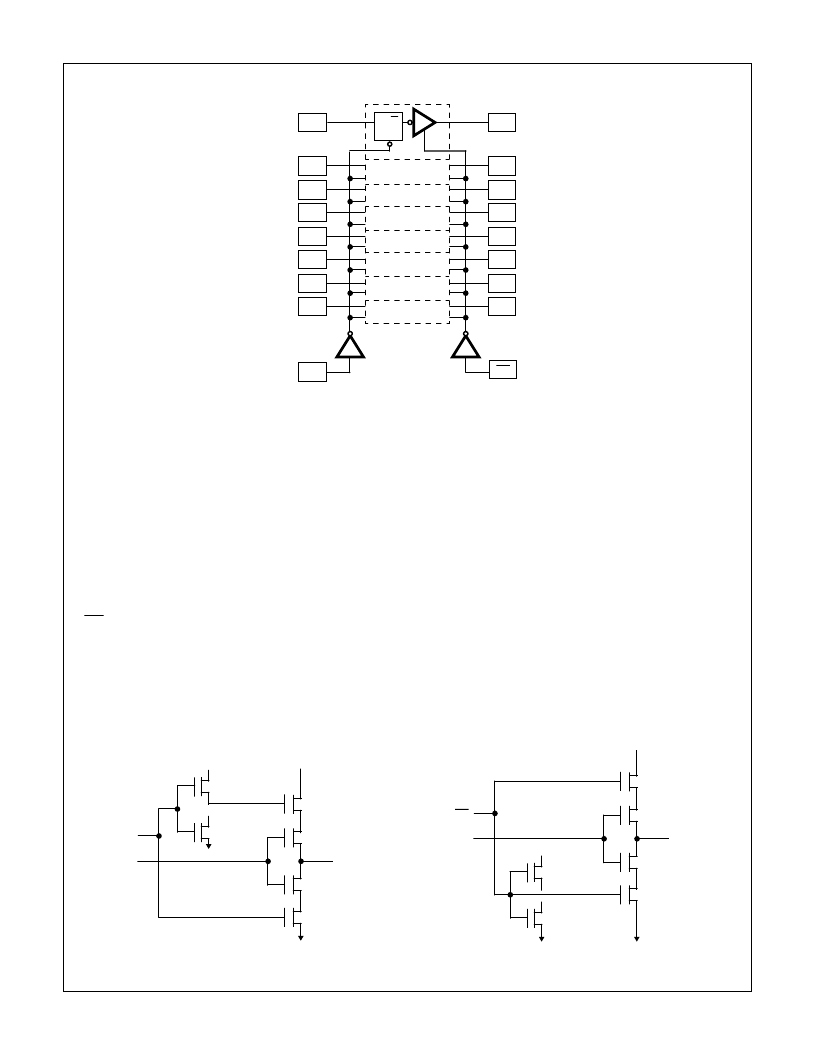

Functional Diagram

Gated Inputs

During normal system operation of a latch, signals on the bus

at the device inputs will become high impedance or make

transitions unrelated to the operation of the latch. These unre-

lated input transitions switch the input circuitry and typically

cause an increase in power dissipation in CMOS devices by

creating a low resistance path between V

CC

and GND when

the signal is at or near the input switching threshold. Addition-

ally, if the driving signal becomes high impedance (“float” con-

dition), it could create an indeterminate logic state at the input

and cause a disruption in device operation.

The Intersil 82C8X Series of bus drivers eliminates these con-

ditions by turning off data inputs when data is latched (STB =

logic zero for the 82C82/83H) and when the device is disabled

(OE =

logic one for 82C86H/87H). These gated inputs dis-

connect the input circuitry from the V

CC

and ground power

supply pins by turning off the upper P-channel and lower N-

channel (see Figures 1, 2). No new current flow from V

CC

to

GND occurs during input transitions and invalid logic states

from floating inputs are not transmitted. The next stage is held

to a valid logic level internal to the device.

DC input voltage levels can also cause an increase in ICC if

these input levels approach the minimum V

IH

or maximum

V

IL

conditions. This is due to the operation of the input cir-

cuitry in its linear operating region (partially conducting

state). The 82C8X series gated inputs mean that this condi-

tion will occur only during the time the device is in the trans

parent mode (STB = logic one). ICC remains below the max-

imum ICC standby specification of l0mA during the time

inputs are disabled, thereby, greatly reducing the average

power dissipation of the 82C8X series devices

Typical 82C82 System Example

In a typical 80C86/88 system, the 82C82 is used to latch

multiplexed addresses and the STB input is driven by ALE

(Address Latch Enable) (see Figure 3). The high pulse width

of ALE is approximately 100ns with a bus cycle time of

800ns (80C86/88 at 5MHz). The 82C82 inputs are active

only 12.5% of the bus cycle time. Average power dissipation

related to input transitioning is reduced by this factor also.

DI

O

DI

1

DI

2

DI

3

DI

4

DI

5

DI

6

DI

7

DO

0

DO

1

DO

2

DO

3

DO

4

DO

5

DO

6

DO

7

OE

STB

D Q

CLK

FIGURE 16. 82C82/83H

FIGURE 17. 82C86H/87H GATED INPUTS

P

P

P

N

N

N

STB

DATA IN

INTERNAL

DATA

V

CC

V

CC

P

P

N

N

OE

DATA IN

INTERNAL

DATA

V

CC

P

N

V

CC

82C82

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ID82C83H | CMOS Octal Latching Inverting Bus Driver |

| ID82C84A | RES,CHIP 1/8W 5% 33 OHM |

| ID82C85 | CMOS Static Clock Controller/Generator |

| ID82C86H | CMOS Octal Bus Transceiver |

| ID82C86H-5 | CMOS Octal Bus Transceiver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ID82C82/+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Non-Inverting Buffer/Driver |

| ID82C83H | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CMOS Octal Latching Inverting Bus Driver |

| ID82C83H/+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Inverting Buffer/Driver |

| ID82C84A | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CMOS Clock Generator Driver |

| ID82C84A/+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CPU System Clock Generator |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。