- 您現(xiàn)在的位置:買賣IC網 > PDF目錄360752 > ICS650-11B BroadCom Networking Clock Synthesizer PDF資料下載

參數資料

| 型號: | ICS650-11B |

| 英文描述: | BroadCom Networking Clock Synthesizer |

| 中文描述: | 博通網絡時鐘合成器 |

| 文件頁數: | 1/4頁 |

| 文件大小: | 50K |

| 代理商: | ICS650-11B |

ICS650-11B

BroadCom Networking Clock Synthesizer

MDS 650-11B

C

Integrated Circuit Systems, Inc. 525 Race Street San Jose CA 95126(408)295-9800tel www.icst.com

1

Revision

012005

Printed 11/1

4/04

PRELIMINARY INFORMATION

The ICS650-11B is a low cost, low jitter, high

performance clock synthesizer customized for

BroadCom. Using analog Phase-Locked Loop

(PLL) techniques, the device accepts a 25.0 MHz

clock or fundamental mode crystal input to

produce multiple output clocks of 25.0 MHz,

33.33 MHz, 66.66 MHz, 100.0 MHz, and

133.33 MHz. All output clocks are frequency

locked together. The ICS650-11B outputs all

have 0 ppm synthesis error.

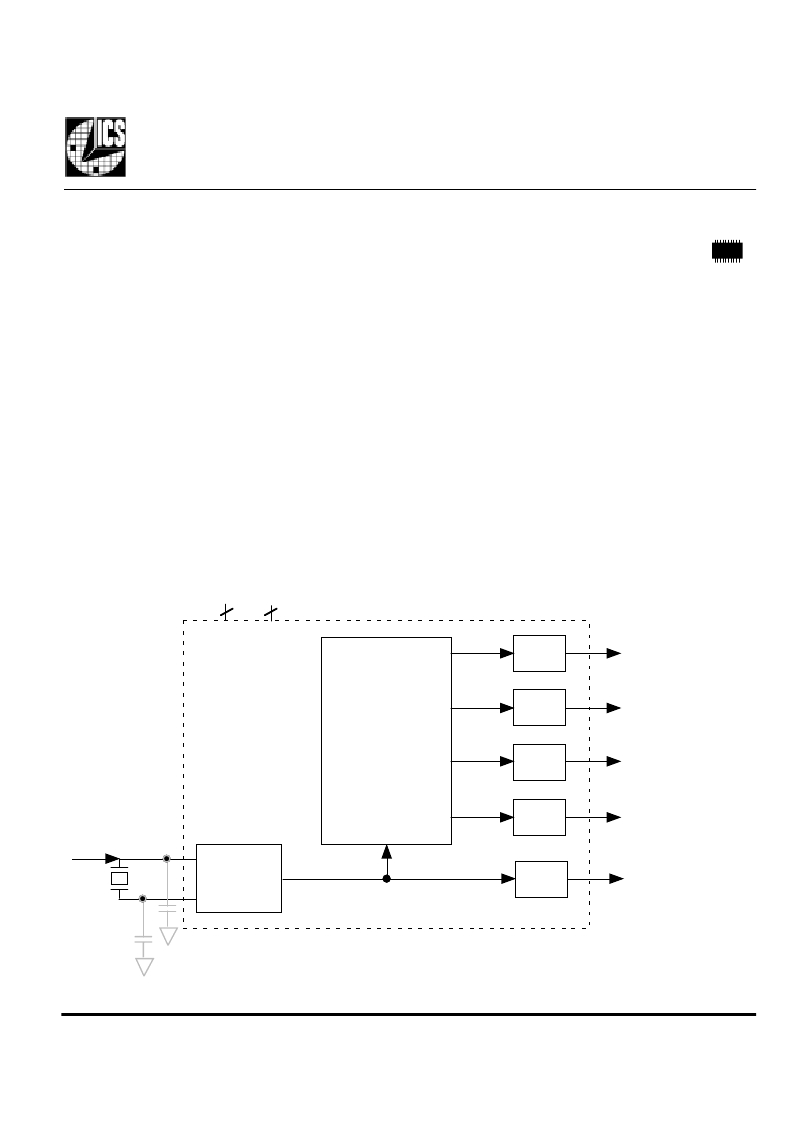

Block Diagram

Description

Features

Packaged in 20 pin narrow SSOP (

Pb free

available

)

25.00 MHz fundamental crystal or clock input

Five fixed output clocks of 25.0 MHz, 33.33 MHz,

66.66 MHz, 100.0 MHz, and 133.33 MHz

Zero ppm synthesis error in all clocks

Ideal for BroadCom BCM5600/BCM5400 chipset

Full CMOS output swing

Advanced, low power, sub-micron CMOS process

3.0V to 5.5V operating voltage

Industrial temperature range

Clock

Buffer/

Crystal

Oscillator

VDD

GND

Clock Synthesis

and Control

Circuitry

133.33 MHz

25.00 MHz

crystal or clock

X1

Output

Buffer

Output

Buffer

66.66 MHz

25.00 MHz

3

5

Output

Buffer

100.0 MHz

Output

Buffer

X2

Output

Buffer

33.33 MHz

Optional crystal capacitors are shown and may be required for tuning of initial accuracy (determined once per board).

相關PDF資料 |

PDF描述 |

|---|---|

| ICS650R-11I | BroadCom Networking Clock Synthesizer |

| ICS650R-11IT | BroadCom Networking Clock Synthesizer |

| ICS650-14B | Networking System Clock |

| ICS650-22 | PVR and STB Clock Source |

| ICS650R-22 | PVR and STB Clock Source |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ICS650-12 | 制造商:ICS 制造商全稱:ICS 功能描述:MPEG Clock Synthesizer |

| ICS650-14B | 制造商:ICS 制造商全稱:ICS 功能描述:Networking System Clock |

| ICS650-21 | 制造商:ICS 制造商全稱:ICS 功能描述:System Peripheral Clock Source |

| ICS650-22 | 制造商:ICS 制造商全稱:ICS 功能描述:PVR and STB Clock Source |

| ICS650-27 | 制造商:ICS 制造商全稱:ICS 功能描述:Networking Clock Source |

發(fā)布緊急采購,3分鐘左右您將得到回復。