- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385433 > HYS72T256220HP-3S-B (QIMONDA AG) 240-Pin Registered DDR2 SDRAM Modules PDF資料下載

參數(shù)資料

| 型號: | HYS72T256220HP-3S-B |

| 廠商: | QIMONDA AG |

| 元件分類: | DRAM |

| 英文描述: | 240-Pin Registered DDR2 SDRAM Modules |

| 中文描述: | 256M X 72 DDR DRAM MODULE, 0.45 ns, DMA240 |

| 封裝: | GREEN, RDIMM-240 |

| 文件頁數(shù): | 27/65頁 |

| 文件大小: | 1429K |

| 代理商: | HYS72T256220HP-3S-B |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當(dāng)前第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁

Internet Data Sheet

Rev. 1.1, 2007-03

03292006-EO3M-LEK7

27

HYS72T[64/128/256]xxxHP–[25F/2.5/3/3S/3.7]–B

240-Pin Registered DDR2 SDRAM

3.3.3

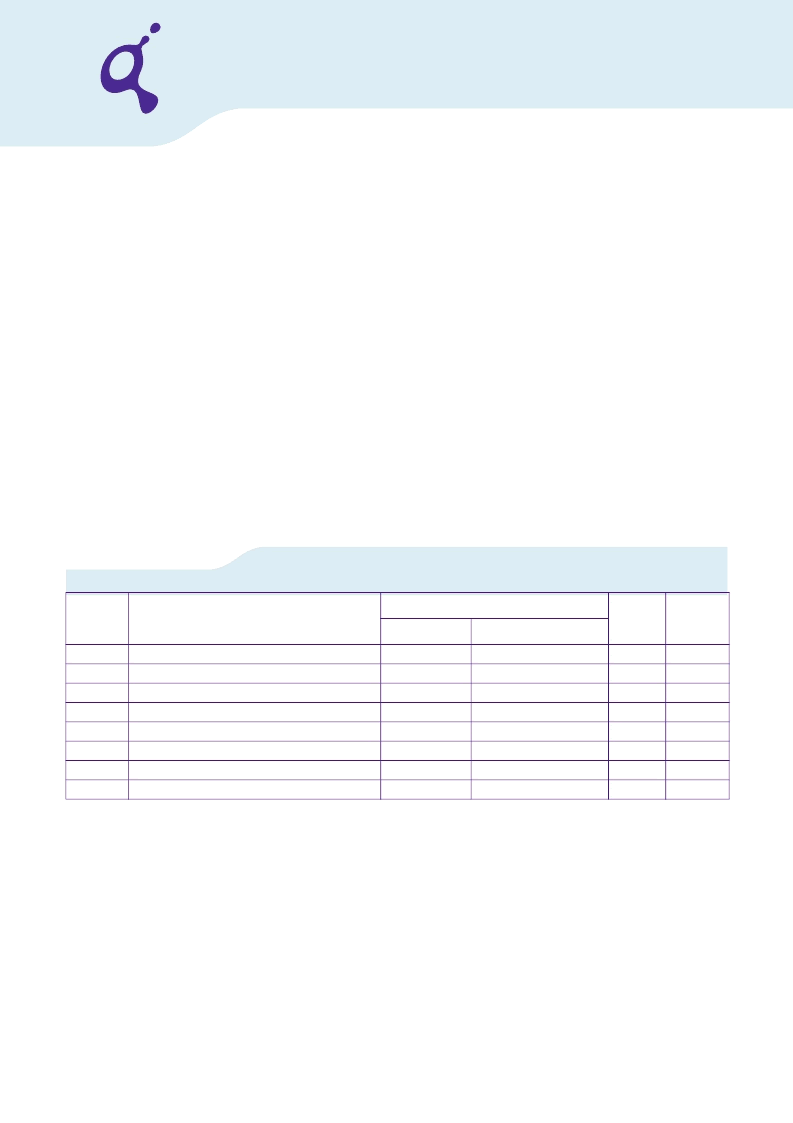

ODT AC Electrical Characteristics

This chapter describes the ODT AC electrical characteristics.

TABLE 18

ODT AC Characteristics and Operating Conditions for DDR2-667 & DDR2-800

13) The

t

HZ

,

t

RPST

and

t

LZ

,

t

RPRE

parameters are referenced to a specific voltage level, which specify when the device output is no longer driving

(

t

t

), or begins driving (

t

t

).

t

and

t

transitions occur in the same access time windows as valid data transitions.These

parameters are verified by design and characterization, but not subject to production test.

14) The Auto-Refresh command interval has be reduced to 3.9 μs when operating the DDR2 DRAM in a temperature range between 85

°

C

and 95

°

C.

15) 0 °C

≤

T

CASE

≤

85

°

C

16) 85

°

C

<

T

CASE

≤

95

°

C

17) A maximum of eight Auto-Refresh commands can be posted to any given DDR2 SDRAM device.

18) The

t

timing parameter depends on the page size of the DRAM organization. See

Table 2 “Ordering Information for RoHS

Compliant Products” on Page 4

.

19) The maximum limit for the

t

parameter is not a device limit. The device operates with a greater value for this parameter, but system

performance (bus turnaround) degrades accordingly.

20) Minimum

t

WTR

is two clocks when operating the DDR2-SDRAM at frequencies

≤ 200 ΜΗ

z.

21) User can choose two different active power-down modes for additional power saving via MRS address bit A12. In “standard active power-

down mode” (MR, A12 = “0”) a fast power-down exit timing

t

XARD

can be used. In “l(fā)ow active power-down mode” (MR, A12 =”1”) a slow

power-down exit timing

t

XARDS

has to be satisfied.

22) WR must be programmed to fulfill the minimum requirement for the

t

timing parameter, where

WR

[cycles] =

t

(ns)/

t

(ns) rounded

up to the next integer value.

t

= WR + (

t

/

t

). For each of the terms, if not already an integer, round to the next highest integer.

t

CK

refers to the application clock period. WR refers to the WR parameter stored in the MRS.

Symbol

Parameter / Condition

Values

Unit

Note

Min.

Max.

t

AOND

t

AON

t

AONPD

t

AOFD

t

AOF

t

AOFPD

t

ANPD

t

AXPD

ODT turn-on delay

ODT turn-on

ODT turn-on (Power-Down Modes)

ODT turn-off delay

ODT turn-off

ODT turn-off (Power-Down Modes)

ODT to Power Down Mode Entry Latency

ODT Power Down Exit Latency

2

t

AC.MIN

t

AC.MIN

+ 2 ns

2.5

t

AC.MIN

t

AC.MIN

+ 2 ns

3

8

2

t

AC.MAX

+ 0.7 ns

2

t

CK +

t

AC.MAX

+ 1 ns

2.5

t

AC.MAX

+ 0.6 ns

2.5

t

CK +

t

AC.MAX

+ 1 ns

—

—

n

CK

ns

ns

n

CK

ns

ns

n

CK

n

CK

1)

1) New units, “

t

CK.AVG

” and “

n

CK

”, are introduced in DDR2-667 and DDR2-800. Unit “

t

CK.AVG

” represents the actual

t

CK.AVG

of the input clock

under operation. Unit “

n

CK

” represents one clock cycle of the input clock, counting the actual clock edges. Note that in DDR2-400 and

DDR2-533, “

t

” is used for both concepts. Example:

t

XP

= 2 [

n

CK

] means; if Power Down exit is registered at

T

m

, an Active command may

be registered at

T

m

+ 2, even if (

T

m

+ 2 -

T

m

) is 2 x

t

CK.AVG

+

t

ERR.2PER(Min)

.

2) ODT turn on time min is when the device leaves high impedance and ODT resistance begins to turn on. ODT turn on time max is when the

ODT resistance is fully on. Both are measured from

t

AOND

, which is interpreted differently per speed bin. For DDR2-667/800,

t

AOND

is 2 clock

cycles after the clock edge that registered a first ODT HIGH counting the actual input clock edges.

3) ODT turn off time min is when the device starts to turn off ODT resistance. ODT turn off time max is when the bus is in high impedance.

Both are measured from

t

AOFD

, which is interpreted differently per speed bin. For DDR2-667/800, if

t

CK(avg)

= 3 ns is assumed,

t

AOFD

is 1.5

ns (= 0.5 x 3 ns) after the second trailing clock edge counting from the clock edge that registered a first ODT LOW and by counting the

actual input clock edges.

1)2)

1)

1)

1)3)

1)

1)

1)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYS72T64000HP-2.5-B | 240-Pin Registered DDR2 SDRAM Modules |

| HYS72T64000HP-25F | 240-Pin Registered DDR2 SDRAM Modules |

| HYS72T64000HP-25F-B | 240-Pin Registered DDR2 SDRAM Modules |

| HYS72T64000HP-3.7-B | 240-Pin Registered DDR2 SDRAM Modules |

| HYS72T64000HP-3-B | 240-Pin Registered DDR2 SDRAM Modules |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYS72T256220HR | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin Registered DDR2 SDRAM Modules |

| HYS72T256220HR-3.7-A | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin Registered DDR2 SDRAM Modules |

| HYS72T256220HR-3.7-B | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin Registered DDR2 SDRAM Modules |

| HYS72T256220HR-3-A | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin Registered DDR2 SDRAM Modules |

| HYS72T256220HR-3S-A | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin Registered DDR2 SDRAM Modules |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。