- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄385433 > HYS72D64300HU-5-C (QIMONDA AG) 184-Pin Unbuffered Double Data Rate SDRAM PDF資料下載

參數(shù)資料

| 型號(hào): | HYS72D64300HU-5-C |

| 廠商: | QIMONDA AG |

| 元件分類: | DRAM |

| 英文描述: | 184-Pin Unbuffered Double Data Rate SDRAM |

| 中文描述: | 64M X 72 DDR DRAM MODULE, 0.5 ns, DMA184 |

| 封裝: | GREEN, UDIMM-184 |

| 文件頁(yè)數(shù): | 16/39頁(yè) |

| 文件大小: | 1052K |

| 代理商: | HYS72D64300HU-5-C |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)當(dāng)前第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)

Internet Data Sheet

Rev. 1.21, 2006-09

03292006-RA8T-MSZL

22

HYS[64/72]D[16/32/128]3xxHU–[5/6]–C

Unbuffered DDR SDRAM Modules

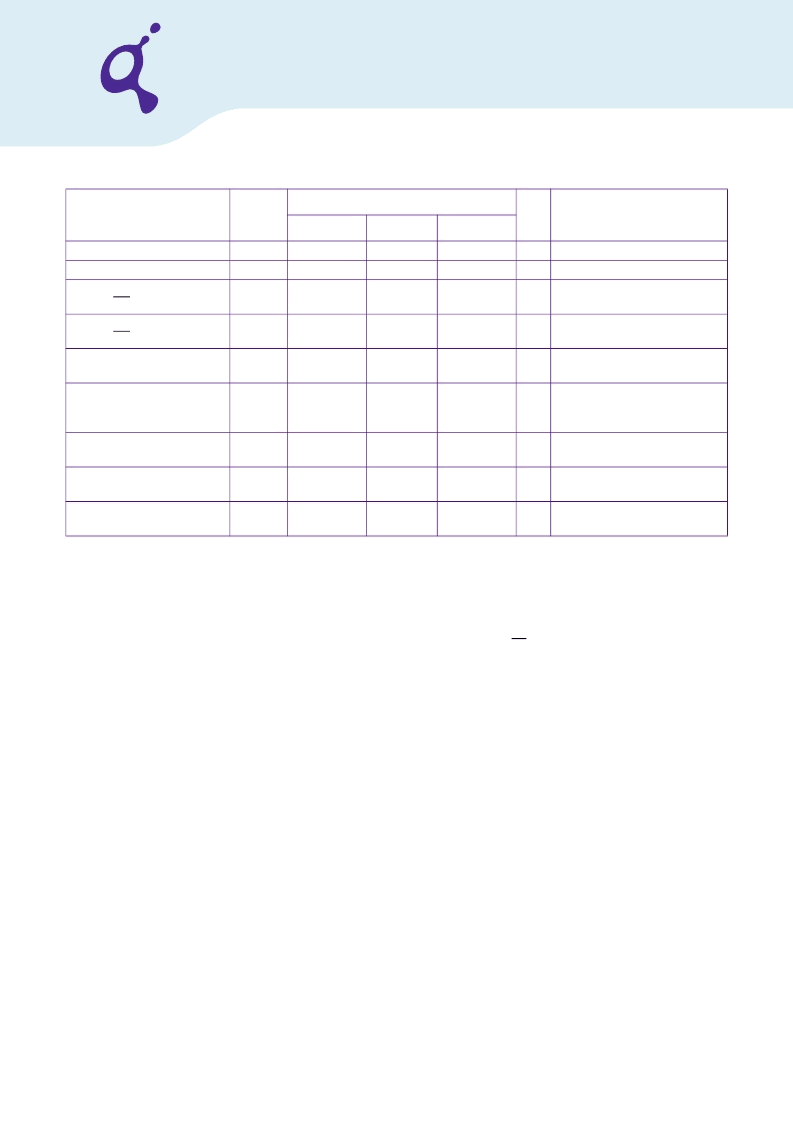

Input High (Logic1) Voltage

Input Low (Logic0) Voltage

Input Voltage Level,

CK and CK Inputs

Input Differential Voltage,

CK and CK Inputs

VI-Matching Pull-up Current

to Pull-down Current

Input Leakage Current

V

IH(DC)

V

IL(DC)

V

IN(DC)

V

REF

+ 0.15

–

0.3

–

0.3

V

DDQ

+ 0.3

V

REF

– 0.15

V

DDQ

+ 0.3

V

V

V

6)

6)

6)

V

ID(DC)

0.36

V

DDQ

+ 0.6

V

6)7)

VI

Ratio

0.71

1.4

—

8)

I

I

–2

2

μ

A

Any input 0 V

≤

V

IN

≤

V

DD

;

All other pins not under test

= 0 V

9)

DQs are disabled;

0 V

≤

V

OUT

≤

V

DDQ

9)

V

OUT

=

1.95 V

Output Leakage Current

I

OZ

–5

5

μ

A

Output High Current, Normal

Strength Driver

Output Low Current, Normal

Strength Driver

1) 0

°

C

≤

T

A

≤

70

°

C; V

DDQ

= 2.5 V

±

0.2 V, V

DD

= +2.5 V

±

0.2 V; VDDQ = 2.6 V ± 0.1 V, VDD = +2.6 V ± 0.1 V (DDR400);

2) DDR400 conditions apply for all clock frequencies above 166 MHz

3) Under all conditions, V

DDQ

must be less than or equal to V

DD

.

4) Peak to peak AC noise on V

REF

may not exceed ± 2% VREF (DC). VREF is also expected to track noise variations in V

DDQ

.

5) V

is not applied directly to the device. V

TT

is a system supply for signal termination resistors, is expected to be set equal to V

REF

, and

must track variations in the DC level of V

REF

.

6) Inputs are not recognized as valid until V

REF

stabilizes.

7) V

ID

is the magnitude of the difference between the input level on CK and the input level on CK.

8) The ratio of the pull-up current to the pull-down current is specified for the same temperature and voltage, over the entire temperature and

voltage range, for device drain to source voltage from 0.25 to 1.0 V. For a given output, it represents the maximum difference between

pull-up and pull-down drivers due to process variation.

9) Values are shown per pin.

I

OH

—

–16.2

mA

I

OL

16.2

—

mA

V

OUT

= 0.35 V

Parameter

Symbol

Values

Unit

Note/Test Condition

1)

Min.

Typ.

Max.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYS72D64300HU-6-C | 184-Pin Unbuffered Double Data Rate SDRAM |

| HYS72D64301HBR_07 | 184-Pin Registered Double-Data-Rate SDRAM Module |

| HYS72D64301HBR-5-C | 184-Pin Registered Double-Data-Rate SDRAM Module |

| HYS72D64301HBR-6-C | 184-Pin Registered Double-Data-Rate SDRAM Module |

| HYS72D64301HBR-6-B | 184 - Pin Registered Double-Data-Rate SDRAM Module |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYS72D64300HU-6-B | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:184-Pin Unbuffered Dual-In-Line Memory Modules |

| HYS72D64300HU-6-C | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:184-Pin Unbuffered Double Data Rate SDRAM |

| HYS72D64301 | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:184 - Pin Registered Double-Data-Rate SDRAM Module |

| HYS72D64301GBR-5-B | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:184 - Pin Registered Double-Data-Rate SDRAM Module |

| HYS72D64301GBR-6-B | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:184 - Pin Registered Double-Data-Rate SDRAM Module |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。