- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385432 > HYB18H256321BF-14 (QIMONDA AG) 256-Mbit GDDR3 Graphics RAM GDDR3 Graphics RAM PDF資料下載

參數(shù)資料

| 型號: | HYB18H256321BF-14 |

| 廠商: | QIMONDA AG |

| 元件分類: | DRAM |

| 英文描述: | 256-Mbit GDDR3 Graphics RAM GDDR3 Graphics RAM |

| 中文描述: | 8M X 32 SYNCHRONOUS GRAPHICS RAM MODULE, 0.25 ns, PBGA136 |

| 封裝: | GREEN, PLASTIC, TFBGA-136 |

| 文件頁數(shù): | 33/41頁 |

| 文件大小: | 1302K |

| 代理商: | HYB18H256321BF-14 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁當(dāng)前第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁

HYB18H256321BF

256-Mbit GDDR3

Internet Data Sheet

Rev. 0.80, 2007-09

09132007-07EM-7OYI

33

4.11

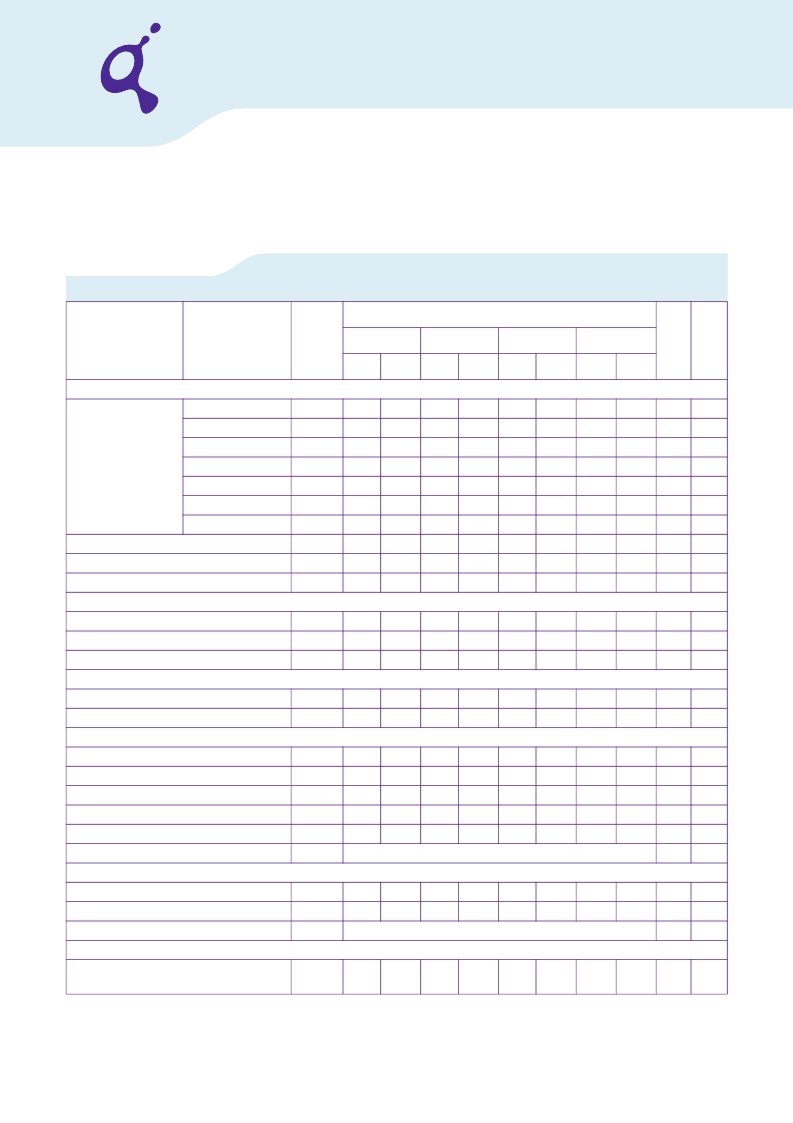

AC Timings for HYB18H256321BF

TABLE 19

Timing Parameters for HYB18H256321BF

Parameter

CAS latency

Symbol Limit Values

Unit

Note

–10

–11

–12

–14

Min.

Max.

Min.

Max.

Min.

Max.

Min.

Max.

Clock and Clock Enable

System frequency

CL=13

CL= 12

CL= 11

CL =10

CL = 9

CL = 8

CL = 7

f

CK13

f

CK12

f

CK11

f

CK10

f

CK9

f

CK8

f

CK7

t

CH

t

CL

t

HP

—

TBD

400

400

400

400

400

0.45

0.45

0.45

—

1000

900

800

700

600

550

0.55

0.55

—

—

—

400

400

400

400

400

0.45

0.45

0.45

—

—

900

800

700

600

550

0.55

0.55

—

—

—

400

400

400

400

400

0.45

0.45

0.45

—

—

800

700

650

550

500

0.55

0.55

—

—

—

400

400

400

400

400

0.45

0.45

0.45

—

—

700

650

600

500

450

0.55

0.55

—

MHz

MHz

MHz

MHz

MHz

MHz

MHz

t

CK

t

CK

t

CK

1)

2)

1)

1)

1)

1)

Clock high level width

Clock low-level width

Minimum clock half period

Command and Address Setup and Hold Timing

Address/Command input setup time

Address/Command input hold time

Address/Command input pulse width

Mode Register Set Timing

Mode Register Set cycle time

Mode Register Set to READ timing

Row Timing

Row Cycle Time

Row Active Time

ACT(a) to ACT(b) Command period

Row Precharge Time

Row to Column Delay Time for Reads

Row to Column Delay Time for Writes

Column Timing

CAS(a) to CAS(b) Command period

Write to Read Command Delay

Read to Write command delay

Write Cycle Timing Parameters for Data and Data Strobe

Write command to first WDQS latching

transition

3)

t

IS

t

IH

t

IP

0.24

0.24

0.7

—

—

—

0.27

0.27

0.7

—

—

—

0.3

0.3

0.7

—

—

—

0.35

0.35

0.7

—

—

—

ns

ns

t

CK

t

MRD

t

MRDR

6

12

—

—

6

12

—

—

6

12

—

—

6

12

—

—

t

CK

t

CK

4)5)

3)

t

RC

t

RAS

t

RRD

t

RP

t

RCDRD

t

RCDWR

37

23

9

14

13

t

RCDWR(Min)

= max(

t

RCDRD(Min)

- (WL + 1)

×

t

CK

;2

×

t

CK

)

—

—

—

—

—

35

22

8

13

12

—

—

—

—

—

34

21

8

13

12

—

—

—

—

—

30

18

7

12

11

—

—

—

—

—

t

CK

t

CK

t

CK

t

CK

t

CK

t

CK

6)

7)

t

CCD

t

WTR

t

RTW

2

7

t

RTW

(min)= (CL + BL/2 +2 -WL)

—

—

2

6

—

—

2

6

—

—

2

5

—

—

t

CK

t

CK

t

CK

8)

9)

10)

t

DQSS

WL–

0.25

WL+

0.25

WL–

0.25

WL+

0.25

WL–

0.25

WL+

0.25

WL–

0.25

WL+

0.25

t

CK

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYB18H512321BF | 512-Mbit GDDR3 Graphics RAM |

| HYB18L128160BF | DRAMs for Mobile Applications 128-Mbit Mobile-RAM |

| HYB18L256160B | DRAMs for Mobile Applications 256-Mbit Mobile-RAM |

| HYMP112S64LMP8-C4 | DDR2 SDRAM SO-DIMM |

| HYMP112S64LMP8-C5 | DDR2 SDRAM SO-DIMM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYB18H512321BF | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:512-Mbit GDDR3 Graphics RAM |

| HYB18H512321BF-08/10 | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:512-Mbit GDDR3 Graphics RAM |

| HYB18H512321BF-11/12/14 | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:512-Mbit GDDR3 Graphics RAM |

| HYB18L128160BC-7.5 | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:DRAMs for Mobile Applications 128-Mbit Mobile-RAM |

| HYB18L128160BC-75 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:DRAMs for Mobile Applications |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。