- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385427 > HY5DU561622DTP-X (Hynix Semiconductor Inc.) 256M DDR SDRAM (268,435,456-bit CMOS Double Data Rate(DDR) Synchronous DRAM) PDF資料下載

參數(shù)資料

| 型號: | HY5DU561622DTP-X |

| 廠商: | Hynix Semiconductor Inc. |

| 英文描述: | 256M DDR SDRAM (268,435,456-bit CMOS Double Data Rate(DDR) Synchronous DRAM) |

| 中文描述: | 256M DDR內(nèi)存(268435456位CMOS雙數(shù)據(jù)速率(DDR)同步DRAM) |

| 文件頁數(shù): | 17/37頁 |

| 文件大?。?/td> | 414K |

| 代理商: | HY5DU561622DTP-X |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

Rev. 0.1 /May 2004 17

HY5DU56422D(L)TP

HY5DU56822D(L)TP

HY5DU561622D(L)TP

7.

Issue 2 or more Auto Refresh commands.

8.

Issue a Mode Register Set command to initialize the mode register with bit A8 = Low.

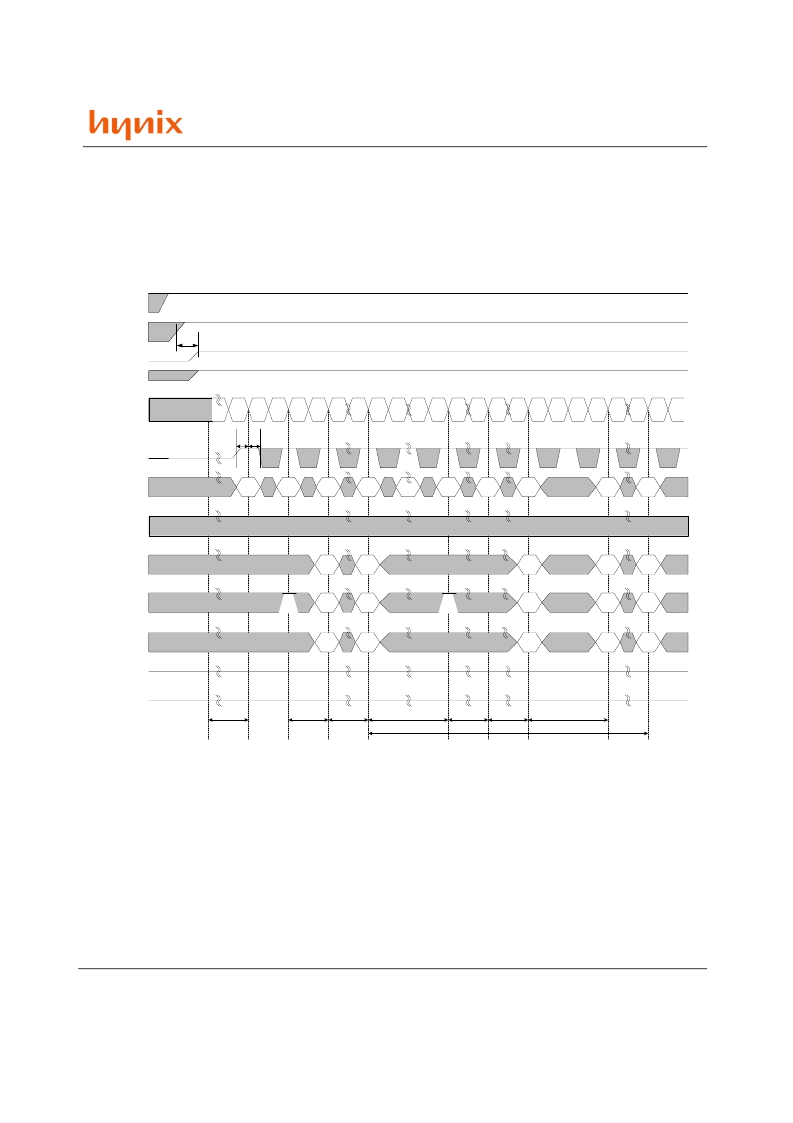

Power-Up Sequence

CODE

CODE

CODE

CODE

CODE

CODE

CODE

CODE

CODE

CODE

CODE

CODE

CODE

CODE

CODE

NOP

PRE

MRS

EMRS

PRE

NOP

MRS

AREF

ACT

RD

VDD

VDDQ

VTT

VREF

/CLK

CLK

CKE

CMD

DM

ADDR

A10

BA0, BA1

DQS

DQ'S

LVCMOS Low Level

tIS tIH

tVTD

T=200usec

tRP

tMRD

tRP

tRFC

tMRD

tXSRD*

READ

Non-Read

Command

VDDPower UP

Precharge All

EMRS Set

MRS Set

(with A8=H)

Precharge All

2 or more

Auto Refresh

MRS Set

(with A8=L)

* 200 cycle(tXSRD) of CK are required (for DLL locking) before Read Command

tMRD

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HY5DU56422DLTP | 256M DDR SDRAM (268,435,456-bit CMOS Double Data Rate(DDR) Synchronous DRAM) |

| HY5DU56422DLTP-H | 256M DDR SDRAM (268,435,456-bit CMOS Double Data Rate(DDR) Synchronous DRAM) |

| HY5DU56422DLTP-J | 256M DDR SDRAM (268,435,456-bit CMOS Double Data Rate(DDR) Synchronous DRAM) |

| HY5DU56422DLTP-K | 256M DDR SDRAM (268,435,456-bit CMOS Double Data Rate(DDR) Synchronous DRAM) |

| HY5DU56422DLTP-L | 256M DDR SDRAM (268,435,456-bit CMOS Double Data Rate(DDR) Synchronous DRAM) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HY5DU561622EFP | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:256Mb DDR SDRAM |

| HY5DU561622EFP-D43-C | 制造商:SK Hynix Inc 功能描述: |

| HY5DU561622EFP-D43DR-C | 制造商:SK Hynix Inc 功能描述: |

| HY5DU561622ELFP | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:256Mb DDR SDRAM |

| HY5DU561622ELFP-D43 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:256Mb DDR SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。