- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385427 > HY5DU561622DTP-M (HYNIX SEMICONDUCTOR INC) 256M DDR SDRAM (268,435,456-bit CMOS Double Data Rate(DDR) Synchronous DRAM) PDF資料下載

參數(shù)資料

| 型號: | HY5DU561622DTP-M |

| 廠商: | HYNIX SEMICONDUCTOR INC |

| 元件分類: | DRAM |

| 英文描述: | 256M DDR SDRAM (268,435,456-bit CMOS Double Data Rate(DDR) Synchronous DRAM) |

| 中文描述: | 16M X 16 DDR DRAM, 0.75 ns, PDSO66 |

| 封裝: | 0.400 X 0.875 INCH, 0.65 MM PITCH, LEAD FREE, TSOP2-66 |

| 文件頁數(shù): | 36/37頁 |

| 文件大小: | 414K |

| 代理商: | HY5DU561622DTP-M |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁當前第36頁第37頁

Rev. 0.1 /May 2004 36

HY5DU56422D(L)TP

HY5DU56822D(L)TP

HY5DU561622D(L)TP

CAPACITANCE

(T

A

=25

o

C, f=100MHz )

Note :

1. VDD = min. to max., VDDQ = 2.3V to 2.7V, V

O

DC = VDDQ/2, V

O

peak-to-peak = 0.2V

2. Pins not under test are tied to GND.

3. These values are guaranteed by design and are tested on a sample basis only.

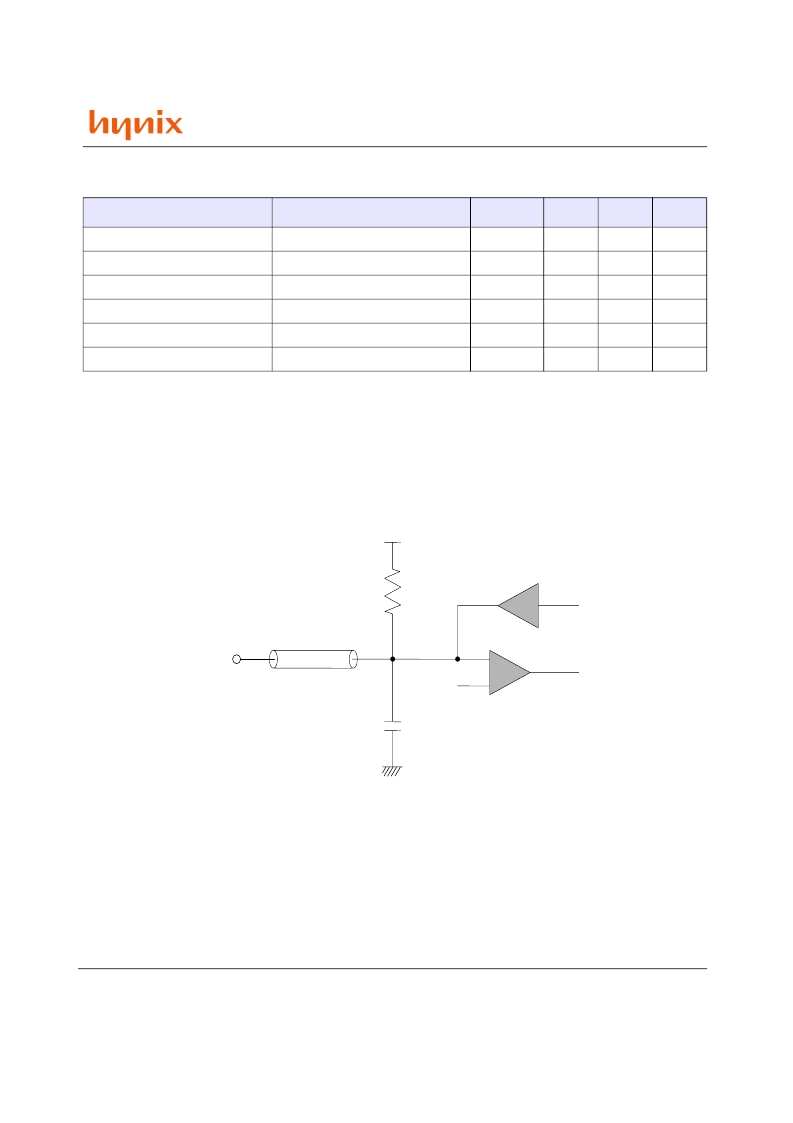

OUTPUT LOAD CIRCUIT

Parameter

Pin

Symbol

Min

Max

Unit

Input Clock Capacitance

CK, /CK

C

I1

2.0

3.0

pF

Delta Input Clock Capacitance

CK, /CK

Delta C

I1

-

0.25

pF

Input Capacitance

All other input-only pins

C

I1

2.0

3.0

pF

Delta Input Capacitance

All other input-only pins

Delta C

I2

-

0.5

pF

Input / Output Capacitance

DQ, DQS, DM

C

IO

4.0

5.0

pF

Delta Input / Output Capacitance

DQ, DQS, DM

Delta C

IO

-

0.5

pF

V

REF

V

TT

R

T

=50

Zo=50

C

L

=30pF

Output

相關PDF資料 |

PDF描述 |

|---|---|

| HY5DU561622DTP-X | 256M DDR SDRAM (268,435,456-bit CMOS Double Data Rate(DDR) Synchronous DRAM) |

| HY5DU56422DLTP | 256M DDR SDRAM (268,435,456-bit CMOS Double Data Rate(DDR) Synchronous DRAM) |

| HY5DU56422DLTP-H | 256M DDR SDRAM (268,435,456-bit CMOS Double Data Rate(DDR) Synchronous DRAM) |

| HY5DU56422DLTP-J | 256M DDR SDRAM (268,435,456-bit CMOS Double Data Rate(DDR) Synchronous DRAM) |

| HY5DU56422DLTP-K | 256M DDR SDRAM (268,435,456-bit CMOS Double Data Rate(DDR) Synchronous DRAM) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| HY5DU561622DTP-X | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:256M DDR SDRAM (268,435,456-bit CMOS Double Data Rate(DDR) Synchronous DRAM) |

| HY5DU561622EFP | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:256Mb DDR SDRAM |

| HY5DU561622EFP-D43-C | 制造商:SK Hynix Inc 功能描述: |

| HY5DU561622EFP-D43DR-C | 制造商:SK Hynix Inc 功能描述: |

| HY5DU561622ELFP | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:256Mb DDR SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。