- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370632 > HM628512CLRR-5 (Hitachi,Ltd.) 4 M SRAM (512-kword x 8-bit) PDF資料下載

參數(shù)資料

| 型號: | HM628512CLRR-5 |

| 廠商: | Hitachi,Ltd. |

| 元件分類: | SRAM |

| 英文描述: | 4 M SRAM (512-kword x 8-bit) |

| 中文描述: | 四米的SRAM(512 - KWord的× 8位) |

| 文件頁數(shù): | 12/17頁 |

| 文件大?。?/td> | 84K |

| 代理商: | HM628512CLRR-5 |

HM628512C Series

12

Low V

CC

Data Retention Characteristics

(Ta = –20 to +70

°

C)

Parameter

Symbol

Min

Typ

Max

Unit

Test conditions*

3

CS

≥

V

CC

– 0.2 V, Vin

≥

0 V

V

CC

= 3.0 V, Vin

≥

0 V

CS

≥

V

CC

– 0.2 V

V

CC

for data retention

Data retention current

V

DR

I

CCDR

2

—

—

V

—

1*

4

50*

1

μ

A

—

1*

4

15*

2

μ

A

Chip deselect to data retention time

t

CDR

t

R

0

—

—

ns

See retention waveform

Operation recovery time

Notes: 1. For L-version and 20

μ

A (max.) at Ta = –20 to +40

°

C.

2. For L-SL-version and 3

μ

A (max.) at Ta = –20 to +40

°

C.

3.

CS

controls address buffer,

WE

buffer,

OE

buffer, and Din buffer. In data retention mode, Vin

levels (address,

WE

,

OE

, I/O) can be in the high impedance state.

4. Typical values are at V

CC

= 3.0 V, Ta = +25

°

C and specified loading, and not guaranteed.

5. t

RC

= read cycle time.

t

RC

*

5

—

—

ns

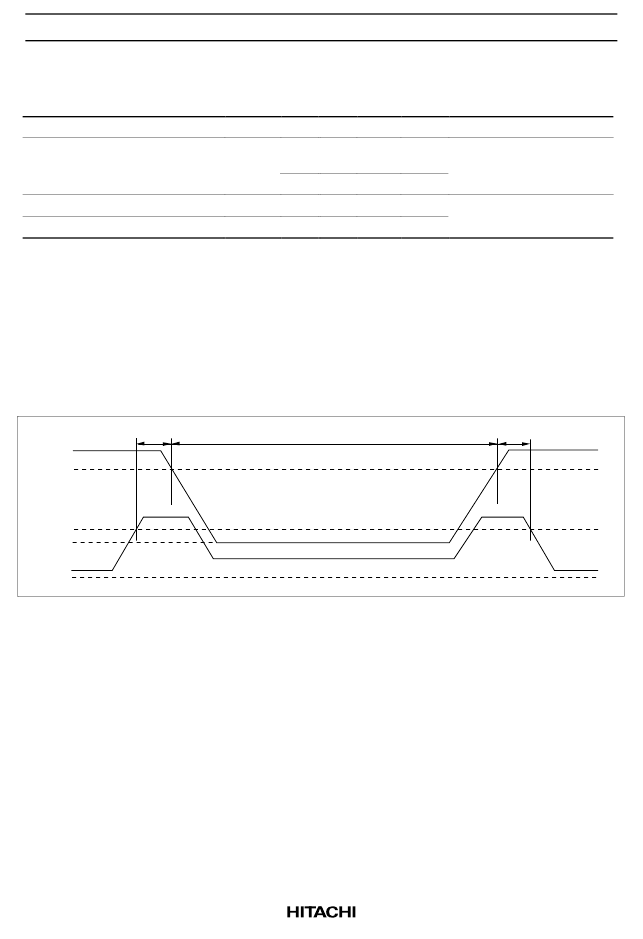

Low V

CC

Data Retention Timing Waveform

(

CS

Controlled)

V

CC

4.5 V

2.2 V

V

DR

0 V

CS

t

CDR

t

R

CS

≥

V

CC

– 0.2 V

Data retention mode

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HM628512CLTT-5 | 4 M SRAM (512-kword x 8-bit) |

| HM628512C | Octal Buffers And Line Drivers With 3-State Outputs 20-CFP -55 to 125 |

| HM628512CLP-5 | 4 M SRAM (512-kword x 8-bit) |

| HM628512CLP-5SL | 4 M SRAM (512-kword x 8-bit) |

| HM628512CLP-7 | 4 M SRAM (512-kword x 8-bit) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HM628512CLRR-5SL | 制造商:HITACHI 制造商全稱:Hitachi Semiconductor 功能描述:4 M SRAM (512-kword x 8-bit) |

| HM628512CLRR-7 | 制造商:Renesas Electronics Corporation 功能描述: |

| HM628512CLRR-7SL | 制造商:HITACHI 制造商全稱:Hitachi Semiconductor 功能描述:4 M SRAM (512-kword x 8-bit) |

| HM628512CLRRI-7 | 制造商:HITACHI 制造商全稱:Hitachi Semiconductor 功能描述:Wide Temperature Range Version 4 M SRAM (512-kword x 8-bit) |

| HM628512CLTT-5 | 制造商:HITACHI 制造商全稱:Hitachi Semiconductor 功能描述:4 M SRAM (512-kword x 8-bit) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。