- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371807 > HFA3783 (HARRIS SEMICONDUCTOR) 288 MACROCELL 3.3 VOLT ISP CPLD PDF資料下載

參數(shù)資料

| 型號(hào): | HFA3783 |

| 廠商: | HARRIS SEMICONDUCTOR |

| 元件分類: | 衰減器 |

| 英文描述: | 288 MACROCELL 3.3 VOLT ISP CPLD |

| 中文描述: | 70 MHz - 600 MHz RF/MICROWAVE I/Q MODEM |

| 文件頁(yè)數(shù): | 11/34頁(yè) |

| 文件大小: | 608K |

| 代理商: | HFA3783 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)當(dāng)前第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)

11

Operational

Mode

1

0

M(0)

0

M(2) M(3) M(4) M(5) M(6) M(7) M(8)

0

0

0

0

M(13) M(14) M(15)

X

X

Offset

Calibration

1

1

C(0) C(1) C(2) C(3) C(4) C(5) C(6)

0

0

0

0

C(11)

X (Don’t Care)

NOTES:

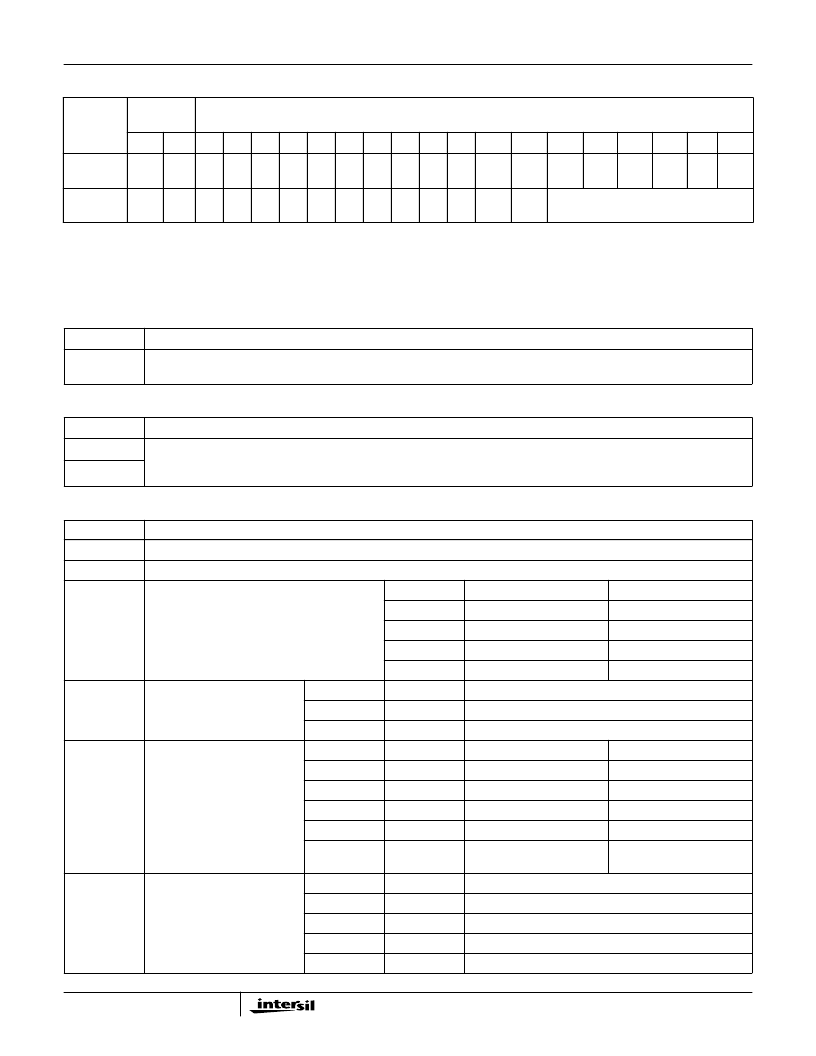

6. The Serial data is clocked on the Rising Edge of the serial clock, MSB first. The serial Interface is active when LE is LOW. The serial Data is

latched into defined registers on the rising edge of LE.

7. The M register or Operational Mode needs to be loaded first. Registers R, A/B and Offset Calibration follow M loading in any sequence.

Reference Frequency Counter/Divider

BIT

DESCRIPTION

R(0-14)

Least significant bit R(0) to most significant bit R(14) of the divide by R counter. The Reference signal frequency is divided down

by this counter and is compared with a divided LO by a phase detector.

LO Frequency Counters/Dividers

BIT

DESCRIPTION

A(0-6)

Least significant bit A(0) to most significant bit A(6) of a 7-bit Swallow counter and LSB B(0) to MSB B(10) of the 11 bits divider.

The LO frequency is divided down by [P

*

B+A], where P is the prescaler divider set by bit M(2). This divided signal frequency is

compared by a phase detector with the divided Reference signal.

B(0-10)

Operational Modes

BIT

DESCRIPTION

M(0)

(PLL_PE), Phase Lock Loop Power Enable. 1 = Enable, 0 = Power Down. Serial port always on.

M(2)

Prescaler Select.

0 = 16/17, 1 = 32/33

M(3)

M(4)

Charge Pump Current Setting.

M(4)

M(3)

OUTPUT SINK/SOURCE

0

0

0.25mA

0

1

0.50mA

1

0

0.75mA

1

1

1.00mA

M(5)

M(6)

Charge Pump Sign.

M(6)

M(5)

0

0

Source Current if LO/ [P

*

B+A] < Ref/R

Source Current if LO/ [P

*

B+A] > Ref/R

M(7)

0

1

M(7)

M(8)

M(13)

LD Pin Multiplex Operation.

M(13)

M(8)

OUTPUT AT PIN LD

0

0

X

Lock Detect Operation

0

1

X

Short to GND

1

0

X

Serial Register Read Back

1

1

0

Ref. Divided by R Waveform

1

1

1

LO Divided by [P

*

B+A]

Waveform

M(14)

M(15)

Charge Pump Operation/Test.

M(15)

M(14)

OPERATION/TEST

0

0

Normal Operation

0

1

Charge Pump Constant Current Source

1

0

Charge Pump Constant Current Sink

1

1

High Impedance State

PLL Synthesizer and DC Offset Clock Programming Table

(Continued)

SERIAL

BITS

REGISTER

DEFINITION

LSB 1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

MSB

HFA3783

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HFA3783IN | I/Q Modulator/Demodulator and Synthesizer |

| HFA3824AIV96 | JT 5C 5#20 PIN WALL RECP |

| HFA3824AIV | Direct Sequence Spread Spectrum Baseband Processor |

| HFA3824A | Direct Sequence Spread Spectrum Baseband Processor |

| HFA3842B | PCMCIA/USB Wireless LAN Medium Access Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HFA3783IN | 制造商:Intersil Corporation 功能描述: |

| HFA3783IN96 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:I/Q Modulator/Demodulator and Synthesizer |

| HFA3824 WAF | 制造商:Harris Corporation 功能描述: |

| HFA3824A | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processor |

| HFA3824AIV | 制造商:Rochester Electronics LLC 功能描述:BASEBAND PROCESSOR - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。