- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371797 > HDMP-1637A 1.25 GBd SerDes Circuit with Differential PECL Clock Inputs for Gigabit Ethernet Applications PDF資料下載

參數(shù)資料

| 型號(hào): | HDMP-1637A |

| 英文描述: | 1.25 GBd SerDes Circuit with Differential PECL Clock Inputs for Gigabit Ethernet Applications |

| 中文描述: | 1.25 GBd的SerDes電路的差分PECL時(shí)鐘輸入的千兆以太網(wǎng)的應(yīng)用 |

| 文件頁數(shù): | 2/12頁 |

| 文件大小: | 177K |

| 代理商: | HDMP-1637A |

2

The design of the HDMP-0421

allows for placement of the CDR

at one of two locations with

respect to a hard disk slot. For

example, if the BYPASS[0]– pin

is HIGH and hard disk slot A is

connected to PBC cell 1, the CDR

function will be performed before

entering the hard disk at slot A

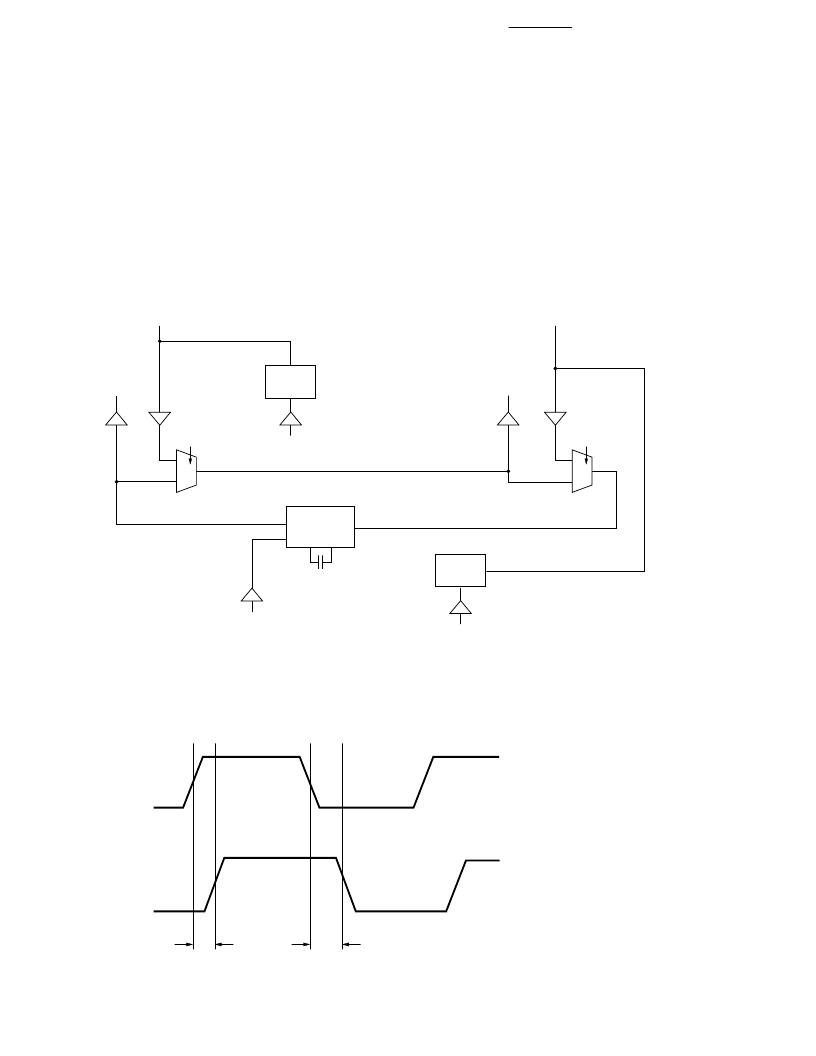

Figure 2. Timing Waveforms.

Figure 1. Block Diagram of HDMP-0421.

(Figure 4). To achieve a CDR

function after slot A, the

BYPASS[1]– pin must be HIGH

and hard disk slot A must be

connected to PBC cell 0

(Figure 5). Table 2 shows both

possible connections. In both

cases, a Signal Detect (SD) pin

shows the status of the signal at

the incoming cable. The

recommended method of setting

the BYPASS[i]– pins HIGH is to

drive them with a high-

impedence signal. Internal pull-

up resistors will force the

BYPASS[I]– pins to V

CC

.

(1) FM_NODE[0]

(2) FM_NODE[4]

(1) TO_NODE[0]

(2) TO_NODE[0]

t

delav1.2

LOSDET

TO_NODE[1]

FM_NODE[1]

BYPASS[1]–

SD[1]

IOSDET

SD[0]

CDR

REFCLK

CEXT

1

0

BYPASS[0]–

1

0

TO_NODE[0]

FM_NODE[0]

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HDMP-1685A | 1.25 Gbps Four Channel SerDes with 5-pin DDR SSTL_2 Parallel Interface |

| HDMP-2501 | Clock/Data Recovery |

| HDMP-2630B | Telecomm/Datacomm |

| HDMP-2631B | Telecomm/Datacomm |

| HDMP-2634 | 1.25 and 2.5 Gbps SerDes Circuits |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HDMP-1638 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Gigabit Ethernet Transceiver Chip with Dual Serial I/O and Differential PECL Clock Inputs |

| HDMP-1646 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Gigabit Ethernet Transceiver Chip |

| HDMP-1646A | 制造商:Agilent 功能描述:_ |

| HDMP1646AG | 制造商:Agilent Technologies 功能描述: |

| HDMP-1685A | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Agilent HDMP-1685A 1.25 Gbps Four Channel SerDes with 5-pin DDR SSTL_2 Parallel Interface |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。