- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370458 > HD404369 (Hitachi,Ltd.) 4-bit HMCS400-Series microcomputer PDF資料下載

參數(shù)資料

| 型號(hào): | HD404369 |

| 廠商: | Hitachi,Ltd. |

| 英文描述: | 4-bit HMCS400-Series microcomputer |

| 中文描述: | 4位HMCS400系列微機(jī) |

| 文件頁(yè)數(shù): | 9/115頁(yè) |

| 文件大小: | 452K |

| 代理商: | HD404369 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)當(dāng)前第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)

HD404369 Series

9

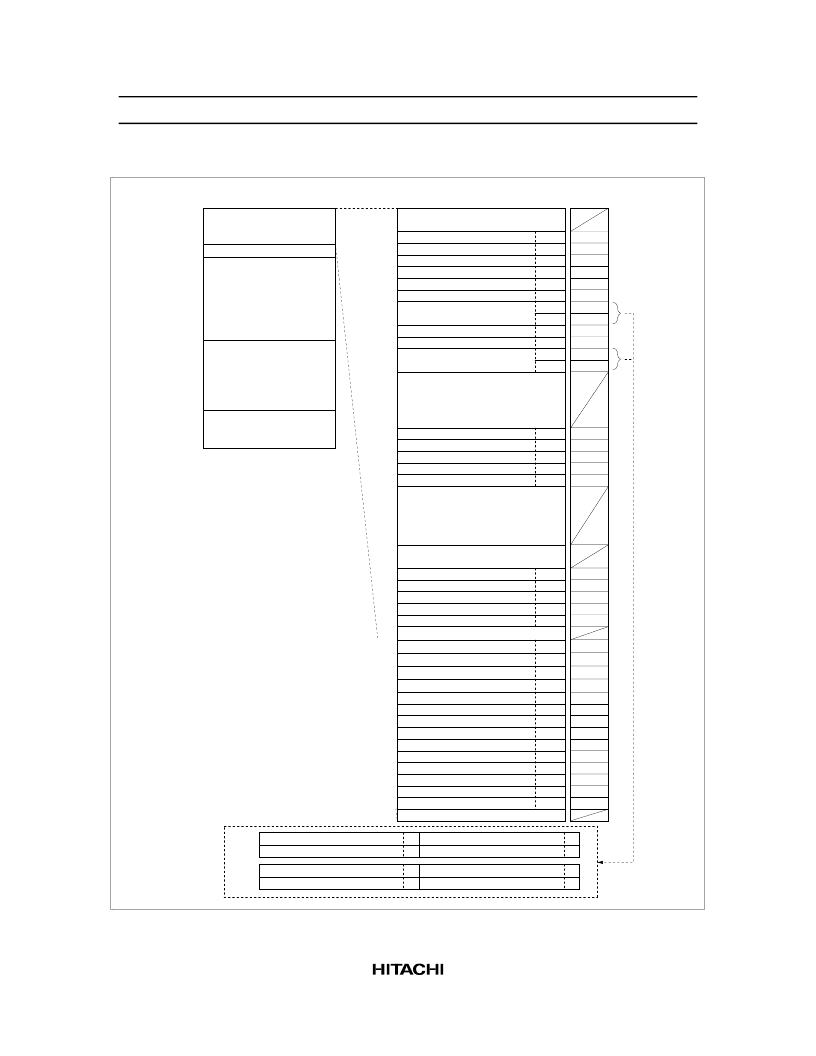

RAM Memory Map

A/D channel register (ACR)

A/D data register lower (ADRL)

A/D data register upper (ADRU)

A/D mode register 1 (AMR1)

A/D mode register 2 (AMR2)

$000

$000

$003

$004

$005

$006

$007

$008

$009

$00A

$00B

$00C

$00D

$00E

$00F

$040

$050

$020

$023

$024

$025

$026

$027

$028

$033

$034

$035

$036

$037

$038

$039

$00A

$00B

$00E

$00F

W

W

R/W

R/W

W

R/W

R/W

W

W

R/W

R/W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

R

R

R

R

W

$3C0

RAM-mapped registers

Memory registers (MR)

Stack (64 digits)

Interrupt control bits area

Port mode register A (PMRA)

Serial mode register (SMR)

Serial data register lower (SRL)

Serial data register upper (SRU)

Timer mode register A (TMA)

Timer mode register B1 (TMB1)

Timer B (TRBL/TWBL)

(TRBU/TWBU)

Miscellaneous register (MIS)

Timer mode register C (TMC)

Timer C (TRCL/TWCL)

(TRCU/TWCU)

Register flag area

Port R0 DCR (DCR0)

Port R1 DCR (DCR1)

Port R2 DCR (DCR2)

Port R3 DCR (DCR3)

Port R4 DCR (DCR4)

Port R5 DCR (DCR5)

Port R6 DCR (DCR6)

Port R7 DCR (DCR7)

Port R8 DCR (DCR8)

Port R9 DCR (DCR9)

Not used

1. Two registers are mapped

on the same area ($00A,

$00B, $00E, $00F).

2. Undefined.

Timer read register B lower (TRBL)

Timer read register B upper (TRBU)

Timer read register C lower (TRCL)

Timer read register C upper (TRCU)

Timer write register B lower (TWBL)

Timer write register B upper (TWBU)

Timer write register C lower (TWCL)

Timer write register C upper (TWCU)

R: Read only

W: Write only

R/W: Read/write

$200

Notes:

$016

$017

$018

$019

$01A

R

R

W

W

$3FF

W

W

W

W

W

W

Port mode register B (PMRB)

Port mode register C (PMRC)

Timer mode register B2 (TMB2)

System clock selection register 1 (SSR1)

System clock selection register 2 (SSR2)

Not used

DCR

DCR

DCR

DCR

$030

$031

$032

Not used

Not used

Not used

0000

0000

1000

0000

-000

0000

0000

Undefined

Undefined

0000

0000

*

2

/0000

Undefined

0000

0000

*

2

/0000

Undefined

0000

0000

0000

0000

0000

0000

0000

-000

0000

0000

0000

00-0

-000

000-

--00

*

1

Initial values

after reset

$03F

Data (432 digits)

0000

0000

0000

--00

Port D

0

–D

3

Port D

4

–D

7

Port D

8

–D

11

Port D

12

, D

13

W

W

W

W

(DCD0)

(DCD1)

(DCD2)

(DCD3)

$02C

$02D

$02E

$02F

Figure 2 RAM Memory Map

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HD404369H | 4-bit HMCS400-Series microcomputer |

| HD404369S | 4-bit HMCS400-Series microcomputer |

| HD404369F | 4-bit HMCS400-Series microcomputer |

| HD404372 | Low-Voltage AS Microcomputers with On-Chip A/D Converter(帶片上A/D轉(zhuǎn)換器的低壓微計(jì)算機(jī)) |

| HD404082 | Low-Voltage AS Microcomputers with On-Chip A/D Converter(帶片上A/D轉(zhuǎn)換器的低壓微計(jì)算機(jī)) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HD404369F | 制造商:HITACHI 制造商全稱:Hitachi Semiconductor 功能描述:4-bit HMCS400-Series microcomputer |

| HD404369H | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:microcomputer has an A/D converter |

| HD404369S | 制造商:HITACHI 制造商全稱:Hitachi Semiconductor 功能描述:4-bit HMCS400-Series microcomputer |

| HD404369SERIES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| HD404372 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:HMCS43XXFamily User's Manual/Device |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。