- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385354 > HC2509C (Hynix Semiconductor Inc.) Motor Driver IC; Supply Voltage Max:18V; Output Current Max:1.6A; Package/Case:10-SIP; Supply Voltage Min:6V PDF資料下載

參數(shù)資料

| 型號: | HC2509C |

| 廠商: | Hynix Semiconductor Inc. |

| 元件分類: | 基準(zhǔn)電壓源/電流源 |

| 英文描述: | Motor Driver IC; Supply Voltage Max:18V; Output Current Max:1.6A; Package/Case:10-SIP; Supply Voltage Min:6V |

| 中文描述: | 鎖相環(huán)時鐘的同步DRAM應(yīng)用分布 |

| 文件頁數(shù): | 1/6頁 |

| 文件大小: | 84K |

| 代理商: | HC2509C |

HC2509C

March 1999

1

HC2509C

Features

l

Phase-Locked Loop Clock Distribution for

Synchronous DRAM Applications

l

Supports PC-100 and Meets “PC100 SDRAM

registered DIMM Specification Rev. 1.2”

l

Distributes One Clock Input to One Bank of Five

and One Bank of Four Outputs

l

No External RC Network Required

l

External Feedback (FBIN) Pin is Used to

Synchronize the Outputs to the Clock Input

l

Separate Output Enable for Each Output Bank

l

Operates at 3.3 V V

cc

l

125 MHz Maximum Frequency

l

On-chip Series Damping Resistors

l

Support Spread Spectrum Clock(SSC)

Synthesizers

l

ESD Protection Exceeds 3000 V per MIL-STD-

883, Method 3015 ; Exceeds 350 V Using

Machine Model ( C = 200 pF, R = 0 )

l

Latch-Up Performance Exceeds 400 mA per

JESD 17

l

Packaged in Plastic 24-Pin Thin Shrink Small-

Outline Package

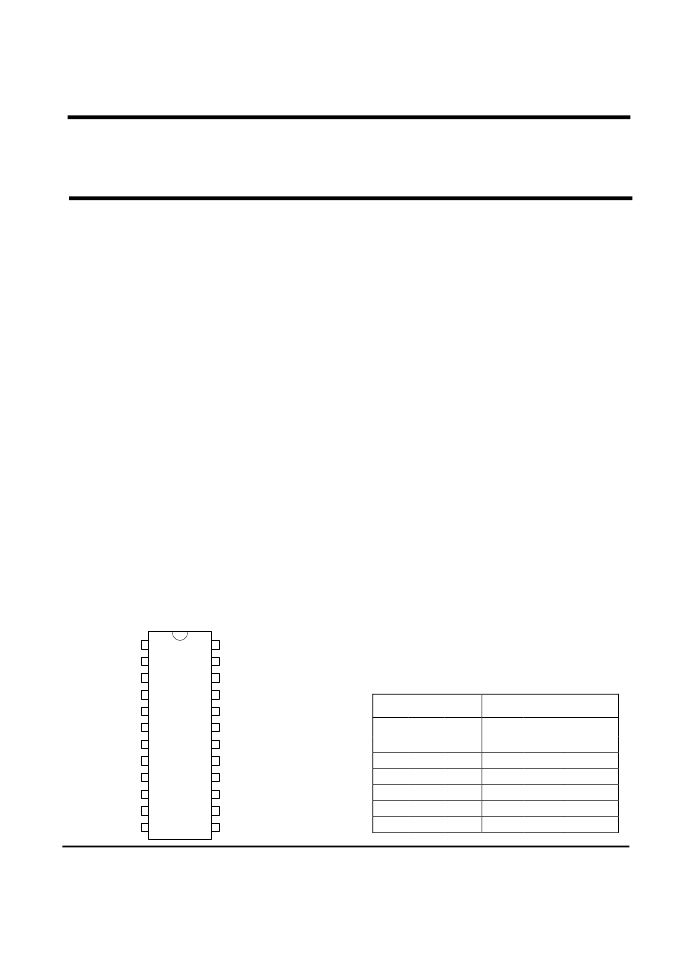

Pin Configuration

General Description

The HC2509C is a low-skew, low jitter, phase-locked

loop(PLL) clock driver, distributing high frequency

clock signals for SDRAM.

The HC2509C operates at 3.3V V

cc

and provides

integrated series-damping resistors that make it ideal

for driving point-to-point loads. The propagation delay

from the CLK input to any clock output is nearly zero.

One bank of five outputs and one bank of four outputs

provide nine low-skew and low-jitter clocks. Each

bank of outputs can be enabled or disabled

separately via the control inputs (1G and 2G). Output

signal duty cycles are adjusted to 50 percent,

independent of the duty cycle at CLK.

The HC2509C is specially designed to interface with

high speed SDRAM applications in the range of

25MHz to 125MHz and includes an internal RC

network which provides excellent jitter characteristics

and eliminates the needs for external components.

For the test purpose, the PLL can be bypassed by

strapping AV

cc

to ground.

The HC2509C is characterized for operation from 0

°

C

to 85

°

C.

Function Table

INPUTS

OUTPUTS

1Y

(0:4)

L

L

L

H

H

2Y

(0:3)

L

L

H

L

H

1G

2G

CLK

FBOUT

X

L

L

H

H

X

L

H

L

H

L

H

H

H

H

L

H

H

H

H

TSSOP 24 PACKAGE

(TOP VIEW)

AGND

Vcc

1Y0

1Y1

1Y2

GND

GND

1Y3

1Y4

Vcc

1G

FBOUT

CLK

AVcc

Vcc

2Y0

2Y1

GND

GND

2Y2

2Y3

Vcc

2G

FBIN

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HC2510 | Phase-Locked Loop Clock Distribution for Synchronous DRAM Applications |

| HC2510C | Voltage Regulator IC; Output Voltage:5.6V; Package/Case:16-DIP; Supply Voltage Max:35V; Output Current Max:500mA; Output Current Min:-500mA; Voltage Regulator Type:PWM; Mounting Type:Through Hole; Supply Voltage Min:8V |

| HC253 | PWM Controller; Mounting Type:Through Hole; Package/Case:18-DIP |

| HC273 | Octal D Flip-Flop with Common Clock and Reset |

| HC365 | Hex 3-State Noninverting Buffer with Common Enables |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HC251 | 制造商:Texas Instruments 功能描述: 制造商:EDSYN 功能描述:Large Hose Extension Coupler ID: 1/4 in. to 1/4 in. |

| HC2510 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:Phase-Locked Loop Clock Distribution for Synchronous DRAM Applications |

| HC2510A | 制造商:MALLORY 功能描述:High Capacity Dry Electrolytic Screw Terminals Capacitor - 1000uF 25dcV -10+150% |

| HC2510C | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:Phase-Locked Loop Clock Distribution for Synchronous DRAM Applications |

| HC2520 | 制造商:AURIS 制造商全稱:AURIS 功能描述:Quartz SMD, Ceramic |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。