- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385354 > HC1-5509A1-5 (INTERSIL CORP) SLIC Subscriber Line Interface Circuit PDF資料下載

參數(shù)資料

| 型號: | HC1-5509A1-5 |

| 廠商: | INTERSIL CORP |

| 元件分類: | 模擬傳輸電路 |

| 英文描述: | SLIC Subscriber Line Interface Circuit |

| 中文描述: | TELECOM-SLIC, CDIP28 |

| 封裝: | CERAMIC, DIP-28 |

| 文件頁數(shù): | 5/10頁 |

| 文件大?。?/td> | 257K |

| 代理商: | HC1-5509A1-5 |

8-135

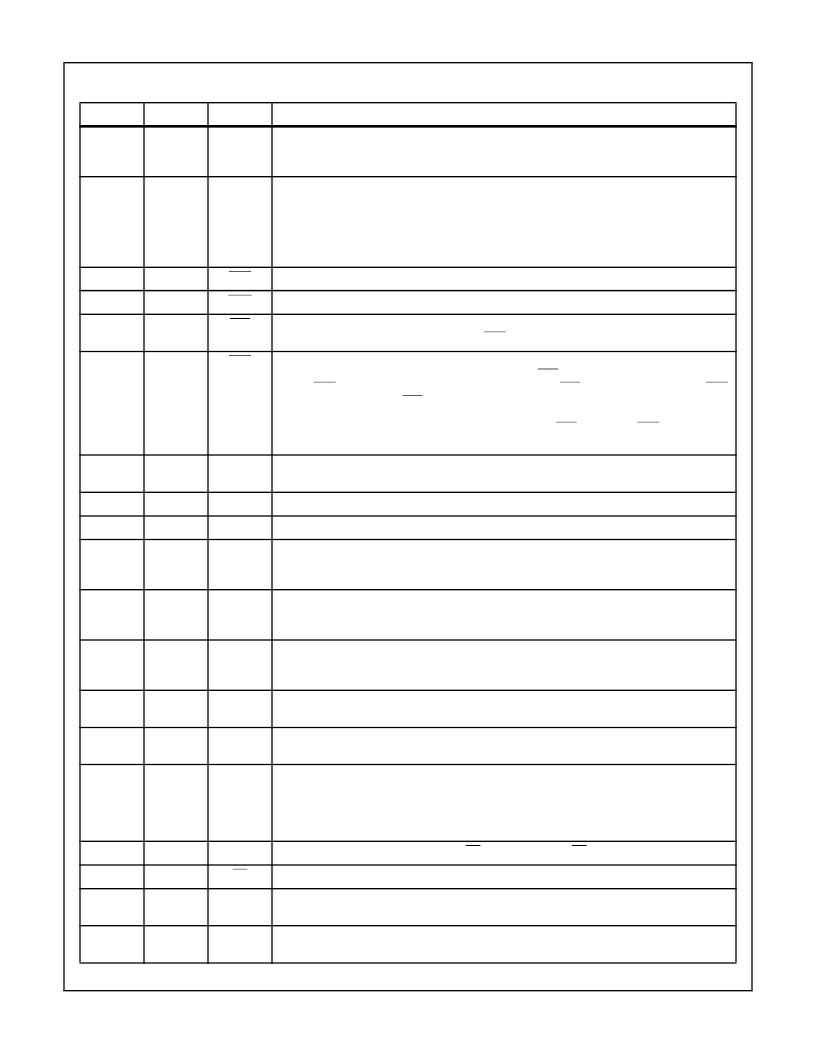

HC-5509A1

5

9

F0

Function Address #0 - A TTL and CMOS compatible input used with F1 function address line to

externally select logic functions. The three selectable functions are mutually exclusive. See Truth

Table on page 1.

6

10

RS

Ring Synchronization Input - A TTL - compatible clock input. The clock is arranged such that a

positive pulse (50 - 500

μ

s) occurs on the zero crossing of the ring voltage source, as it appears

at the RFS terminal. For Tip side injected systems, the RS pulse should occur on the negative

going zero crossing and for Ring injected systems, on the positive going zero crossing. This en-

sures that the ring delay activates and deactivates when the instantaneous ring voltage is near

zero. If synchronization is not required, the pin should be tied to +5.

7

11

SHD

Switch Hook Detection - An active low LS TTL compatible logic output. A line supervisory output.

8

12

GKD

Ground Key Detection - An active low LS TTL compatible logic output. A line supervisory output.

9

13

TST

A TTL logic input. A low on this pin will set a latch and keep the SLIC in a power down mode until

the proper F1, F0 state is set and will keep ALM low. See Truth Table on page 1.

10

14

ALM

A LS TTL compatible active low output which responds to the thermal detector circuit when a safe

operating die temperature has been exceeded. When TST is forced low by an external control

signal, ALM is latched low until the proper F1, F0 state and TST input is brought high. The ALM

can be tied directly to the TST pin to power down the part when a thermal fault is detected and

then reset with F0, F1. See Truth Table on page 1. It is possible to ignore transient thermal over-

load conditions in the SLIC by delaying the response to the TST pin from the ALM. Care must be

exercised in attempting this as continued thermal overstress may reduced component life.

11

18

ILMT

Loop Current Limit - Voltage on this pin sets the short loop current limiting conditions using a re-

sistive voltage divider.

12

19

OUT1

The analog output of the spare operational amplifier.

13

20

-IN1

The inverting analog input of the spare operational amplifier.

14

22

TIP

An analog input connected to the TIP (more positive) side of the subscriber loop through a feed

resistor and ring relay contact. Functions with the RING terminal to receive voice signals from

the telephone and for loop monitoring purpose.

15

24

RING

An analog input connected to the RING (more negative) side of the subscriber loop through a

feed resistor. Functions with the TIP terminal to receive voice signals from the telephone and for

loop monitoring purposes.

16

25

RFS

Ring Feed Sense - Senses RING side of the loop for Ground Key Detection. During Ring injected

ringing the ring signal at this node is isolated from RF via the ring relay. For Tip injected ringing,

the RF and RFS pins must be shorted.

17

27

VRX

Receive Input, Four Wire Side - A high impedance analog input. AC signals appearing at this in-

put drive the Tip Feed and Ring Feed amplifiers differentially.

18

31

LAO

Longitudinal Amplifier Output - A low impedance output to be connected to C2 through a low pass

filter. Output is proportional to the difference in I

TIP

and I

RING

.

19

32

VTX

Transmit Output, Four Wire Side - A low impedance analog output which represents the differ-

ential voltage across TIP and RING. Transhybrid balancing must be performed beyond this out-

put to completely implement two to four wire conversion. This output is referenced to analog

ground. Since the D.C. level of this output varies with loop current, capacitive coupling to the next

stage is necessary.

20

33

PRI

A TTL compatible input used to control PR. PRI active High = PR active low.

21

34

PR

An active low open collector output. Can be used to drive a Polarity Reversal Relay.

NA

35

DG

Digital Ground - To be connected to zero potential - serves as reference for all digital inputs and

outputs on the SLIC.

22

36

BG

Battery Ground - Tube connected to zero potential. All loop current and some quiescent current

flows into this terminal.

Pin Descriptions (Continued)

DIP/SOIC

PLCC

SYMBOL

DESCRIPTION

相關PDF資料 |

PDF描述 |

|---|---|

| HC3-5509A1-5 | SLIC Subscriber Line Interface Circuit |

| HC9P5509A1-5 | SLIC Subscriber Line Interface Circuit |

| HC1-5509A1-9 | SLIC Subscriber Line Interface Circuit |

| HC3-5509A1-9 | SLIC Subscriber Line Interface Circuit |

| HC00 | Quad 2-Input NAND Gate |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| HC1-5509A1-5 WAF | 制造商:Harris Corporation 功能描述: |

| HC1-5509A1-9 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:SLIC Subscriber Line Interface Circuit |

| HC1-5509B-5 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HC1-5509B-9 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HC1-5512-5 | 制造商:Harris Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。