- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385344 > GS9020ACFV (Gennum Corporation) GENLINX -TM II GS9020A Serial Digital Video Input Processor PDF資料下載

參數(shù)資料

| 型號(hào): | GS9020ACFV |

| 廠商: | Gennum Corporation |

| 英文描述: | GENLINX -TM II GS9020A Serial Digital Video Input Processor |

| 中文描述: | GENLINX -商標(biāo)二GS9020A串行數(shù)字視頻輸入處理器 |

| 文件頁數(shù): | 9/31頁 |

| 文件大小: | 258K |

| 代理商: | GS9020ACFV |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當(dāng)前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁

19922 - 3

9 of 31

G

The serial data output circuits are shown in Figure 6. The

serial data outputs are designed to drive 50-75

controlled

impedance traces and can be easily connected to the

GS9028 cable driver as shown in Figure 7 and Figure 18.

Note that to output proper PECL signal levels, a resistor

must be connected between the two serial data outputs.

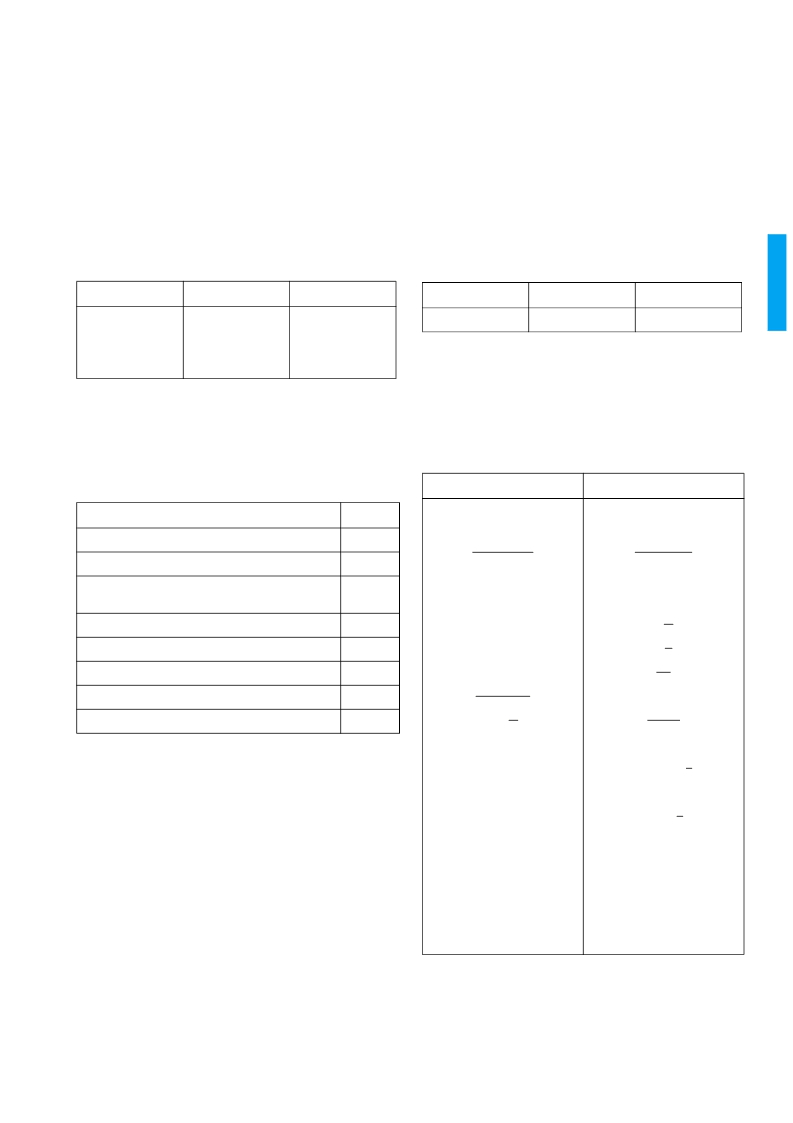

1.4 Automatic Standard Detection

The device automatically detects the incoming video

standard. The detected standard is encoded on the

STD[3:0] pins and the HOSTIF read table bits as shown in

Table 1 and Table 3.

Noise immunity is included to ensure that momentary signal

corruption does not affect the automatic standards

detection function. This built in noise immunity results in

delayed detection time during power up and when

switching between standards. Delays range from as little as

eight lines when switching between component standards

to as much as four frames when switching between PAL

and NTSC standards. If this delay is intolerable, the user

can manually set the standard through the HOSTIF write

table. To set the standard manually, the STD_SEL bit must

be set HIGH and the S bit and STD[3:0] pins/HOSTIF bits

set accordingly. The default standard upon reset of the chip

is NTSC 4:2:2 component (13.5MHz Y sampling).

The S bit, used for single link data standards only, is

encoded in the TRSID word and indicates if the data is in

RGB or YC

R

C

B

format as per SMPTE RP174. In automatic

standard detection mode, the S bit can be read from the

HOSTIF read table. In manual mode, the S bit must be set

in the HOSTIF write table.

1.5 Parallel Clock Output

The PCLKOUT pin provides the output parallel clock. All

synchronous I/O are timed relative to PCLKOUT. The

following listing shows which I/O's are synchronous and

which are not. Timing for synchronous outputs is shown in

Figure 3. Timing for synchronous inputs is shown in

Figure 2.

PIN

LOGIC OPR

HOST BIT

STD_SEL

STD[3:0]

STD[3:0]

S

TABLE 1

STANDARD NAME

STD[3:0]

NTSC 4:2:2 Component with 13.5MHz Y sampling

0000

NTSC Composite

0001

NTSC 4:2:2 16x9 Widescreen with 18MHz Y

sampling

0010

NTSC 4:4:4:4 Single Link with 13.5MHz Y sampling

0011

PAL 4:2:2 Component with 13.5MHz Y sampling

0100

PAL Composite

0101

PAL 4:2:2 16x9 Widescreen with 18MHz Y sampling

0110

PAL 4:4:4:4 Single Link with 13.5MHz Y sampling

0111

PIN

LOGIC OPR

HOST BIT

PCLKOUT

SYNCHRONOUS

ASYNCHRONOUS

FL[4:0]

P[7:5]

S[1:0]

SCL/P4

FIFO_RESET

INTERRUPT

DOUT[9:0]

SDA/P3

F[2:0]

A[2:0]/P[2:0]

V

R/W

H

A/D

ANC_DATA

CS

BLANK_EN

FLAG_MAP

F_R/W

RESET

NO_EDH

CRC_MODE

STD[3:0]

VBLANKS/L

TRS_ERROR

HOSTIF_MODE

FIFOE/S

FLYWDIS

BYPASS_EDH

SDO_MODE

ANC_CHKSM

CLIP_TRS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GS9020ACFVE3 | GENLINX -TM II GS9020A Serial Digital Video Input Processor |

| GS9020ACTV | GENLINX -TM II GS9020A Serial Digital Video Input Processor |

| GS9020ACTVE3 | GENLINX -TM II GS9020A Serial Digital Video Input Processor |

| GS9021A | GENLINX -TM II GS9021A EDH Coprocessor |

| GS9021ACFU | GENLINX -TM II GS9021A EDH Coprocessor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GS9020ACFVE3 | 制造商:Semtech Corporation 功能描述:Video Proc 5V 0.19A 80-Pin LQFP Tray 制造商:Semtech Corporation 功能描述:Serial Digital Video Input Processor |

| GS9020ACTV | 制造商:GENNUM 制造商全稱:GENNUM 功能描述:GENLINX -TM II GS9020A Serial Digital Video Input Processor |

| GS9020ACTVE3 | 制造商:Semtech Corporation 功能描述:Serial Digital Video Input Processor |

| GS9020-CFV | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Serial Digital Video Input Processor |

| GS9020-CTV | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Serial Digital Video Input Processor |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。