- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19907 > EPC16UC88N (Altera)IC CONFIG DEVICE 16MBIT 88-UBGA PDF資料下載

參數(shù)資料

| 型號(hào): | EPC16UC88N |

| 廠商: | Altera |

| 文件頁數(shù): | 11/36頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC CONFIG DEVICE 16MBIT 88-UBGA |

| 產(chǎn)品培訓(xùn)模塊: | Three Reasons to Use FPGA's in Industrial Designs |

| 標(biāo)準(zhǔn)包裝: | 105 |

| 系列: | EPC |

| 可編程類型: | 系統(tǒng)內(nèi)可編程 |

| 存儲(chǔ)容量: | 16Mb |

| 電源電壓: | 3 V ~ 3.6 V |

| 工作溫度: | 0°C ~ 70°C |

| 封裝/外殼: | 88-LFBGA |

| 供應(yīng)商設(shè)備封裝: | 88-UBGA(11x8) |

| 包裝: | 托盤 |

| 產(chǎn)品目錄頁面: | 604 (CN2011-ZH PDF) |

| 其它名稱: | 544-1374 EPC16UC88N-ND |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當(dāng)前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁

Functional Description

Page 19

Enhanced Configuration (EPC) Devices Datasheet

January 2012

Altera Corporation

The general guideline for effectiveness of compression is the higher the device logic or

routing utilization, the lower the compression ratio (where the compression ratio is

defined as the original bitstream size divided by the compressed bitstream size).

For Stratix designs, based on a suite of designs with varying amounts of logic

utilization, the minimum compression ratio was observed to be 1.9 or a ~47% size

reduction for these designs. Table 6 lists sample compression ratios from a suite of

Stratix designs. These numbers serve as a guideline, not a specification, to help you

allocate sufficient configuration memory to store compressed bitstreams.

Programmable Configuration Clock

The configuration clock (DCLK) speed is user programmable. One of two clock sources

can be used to synthesize the configuration clock; a programmable oscillator or an

external clock input pin (EXCLK). The configuration clock frequency can be further

synthesized using the clock divider circuitry. This clock can be divided by the N

counter to generate your DCLK output. The N divider supports all integer dividers

between 1 and 16, as well as a 1.5 divider and a 2.5 divider. The duty cycle for all clock

divisions other than non-integer divisions is 50% (for the non-integer dividers, the

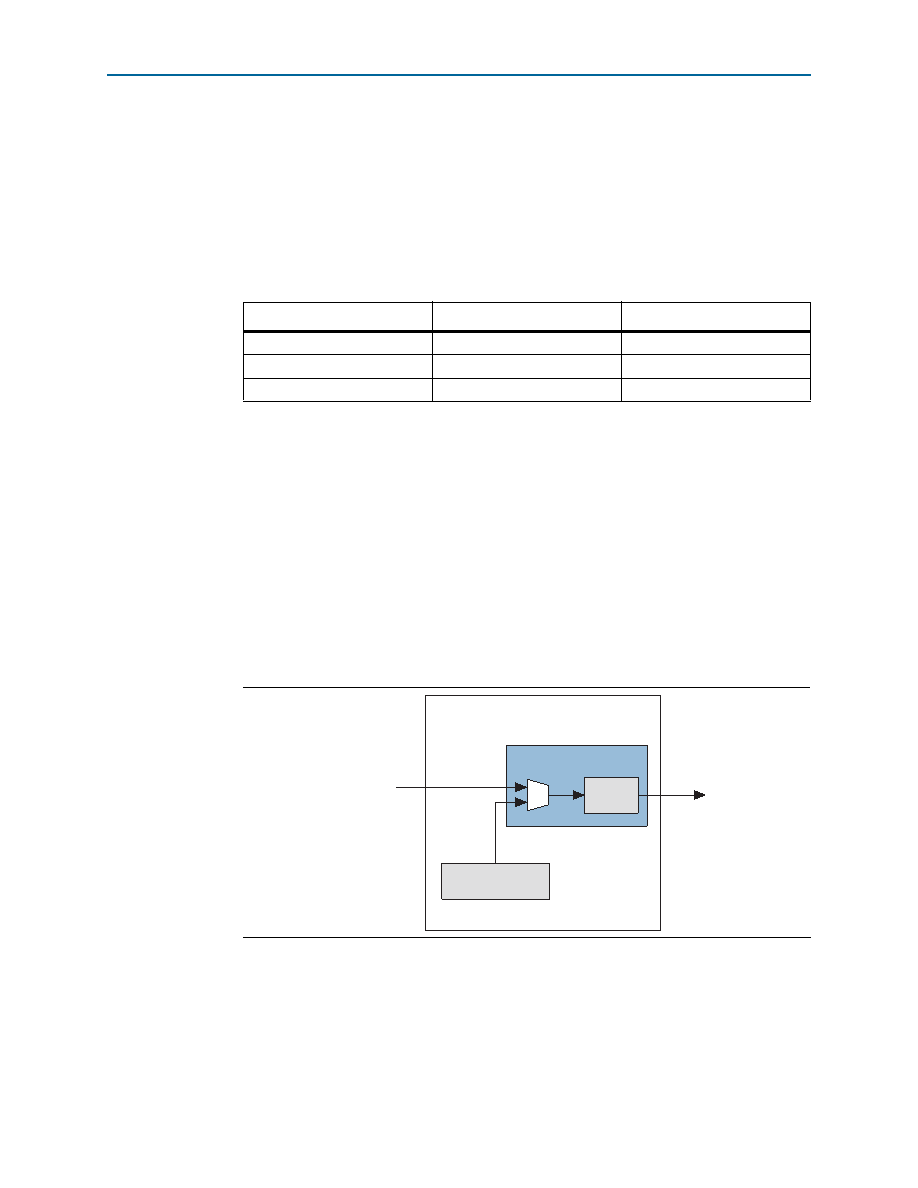

duty cycle will not be 50%). Figure 5 shows a block diagram of the clock divider unit.

The DCLK frequency is limited by the maximum DCLK frequency the FPGA supports.

f For more information about the maximum DCLK input frequency supported by the

FPGA, refer to the configuration chapter in the appropriate device handbook.

Table 6. Stratix Compression Ratios (1)

Item

Minimum

Average

Logic Utilization

98%

64%

Compression Ratio

1.9

2.3

% Size Reduction

47%

57%

Note to Table 6:

(1) These numbers are preliminary. They are intended to serve as a guideline, not a specification.

Figure 5. Clock Divider Unit

Configuration Device

Clock Divider Unit

Divide

by N

External Clock

(Up to 100 MHz)

Internal Oscillator

10 MHz

33 MHz

50 MHz

66 MHz

DCLK

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LTC4301IDD#TR | IC BUFFER BUS HOTSWAP 2WR 8DFN |

| AGM22DTBH | CONN EDGECARD 44POS R/A .156 SLD |

| AYM22DTBD | CONN EDGECARD 44POS R/A .156 SLD |

| V48C8H100BF2 | CONVERTER MOD DC/DC 8V 100W |

| ASM22DTBD | CONN EDGECARD 44POS R/A .156 SLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EPC16UI88AA | 功能描述:FPGA-配置存儲(chǔ)器 IC - Ser. Config Mem Flash 16Mb 33 MHz RoHS:否 制造商:Altera Corporation 存儲(chǔ)類型:Flash 存儲(chǔ)容量:1.6 Mbit 工作頻率:10 MHz 電源電壓-最大:5.25 V 電源電壓-最小:3 V 電源電流:50 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PLCC-20 |

| EPC16UI88N | 功能描述:FPGA-配置存儲(chǔ)器 IC - Ser. Config Mem Flash 16Mb 33 MHz RoHS:否 制造商:Altera Corporation 存儲(chǔ)類型:Flash 存儲(chǔ)容量:1.6 Mbit 工作頻率:10 MHz 電源電壓-最大:5.25 V 電源電壓-最小:3 V 電源電流:50 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PLCC-20 |

| EPC16XXX | 制造商:ALTERA 制造商全稱:Altera Corporation 功能描述:2. Enhanced Configuration Devices (EPC4, EPC8 & EPC16) Data Sheet |

| EPC17 | 制造商:TDK 制造商全稱:TDK Electronics 功能描述:Ferrite Cores For Power Supply and Signal Transformer EPC Cores |

| EPC-17 | 制造商:Curtis Industries 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。