- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄295886 > EP20K60EFC484-3 (ALTERA CORP) LOADABLE PLD, PBGA484 PDF資料下載

參數(shù)資料

| 型號(hào): | EP20K60EFC484-3 |

| 廠商: | ALTERA CORP |

| 元件分類: | PLD |

| 英文描述: | LOADABLE PLD, PBGA484 |

| 封裝: | 23 X 23 MM, 1 MM PITCH, FINE LINE, BGA-484 |

| 文件頁數(shù): | 38/114頁 |

| 文件大小: | 4116K |

| 代理商: | EP20K60EFC484-3 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁當(dāng)前第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁

Altera Corporation

3

Preliminary Information

APEX 20K Programmable Logic Device Family Data Sheet

Note:

(1)

Certain APEX 20K devices are 5.0-V tolerant. See “MultiVolt I/O Interface” on page

46 for details.

s

Advanced interconnect structure

–

Four-level hierarchical FastTrack Interconnect structure

providing fast, predictable interconnect delays

–

Dedicated carry chain that implements arithmetic functions such

as fast adders, counters, and comparators (automatically used by

software tools and megafunctions)

–

Dedicated cascade chain that implements high-speed,

high-fan-in logic functions (automatically used by software tools

and megafunctions)

–

Interleaved local interconnect allows one LE to drive 29 other

LEs through the fast local interconnect

s

Advanced packaging options

–

Available in a variety of packages with 144 to 1,020 pins (see

–

FineLine BGATM packages maximize board space efficiency

–

SameFrameTM pin migration providing migration capability

across device densities and package sizes

s

Advanced software support

–

Software design support and automatic place-and-route

provided by the Altera QuartusTM development system for

Windows-based PCs, Sun SPARCstations, and HP 9000

Series 700/800 workstations

–

Altera MegaCoreTM functions and Altera Megafunction Partners

Program (AMPPSM) megafunctions

–

NativeLinkTM integration with popular synthesis, simulation,

and timing analysis tools

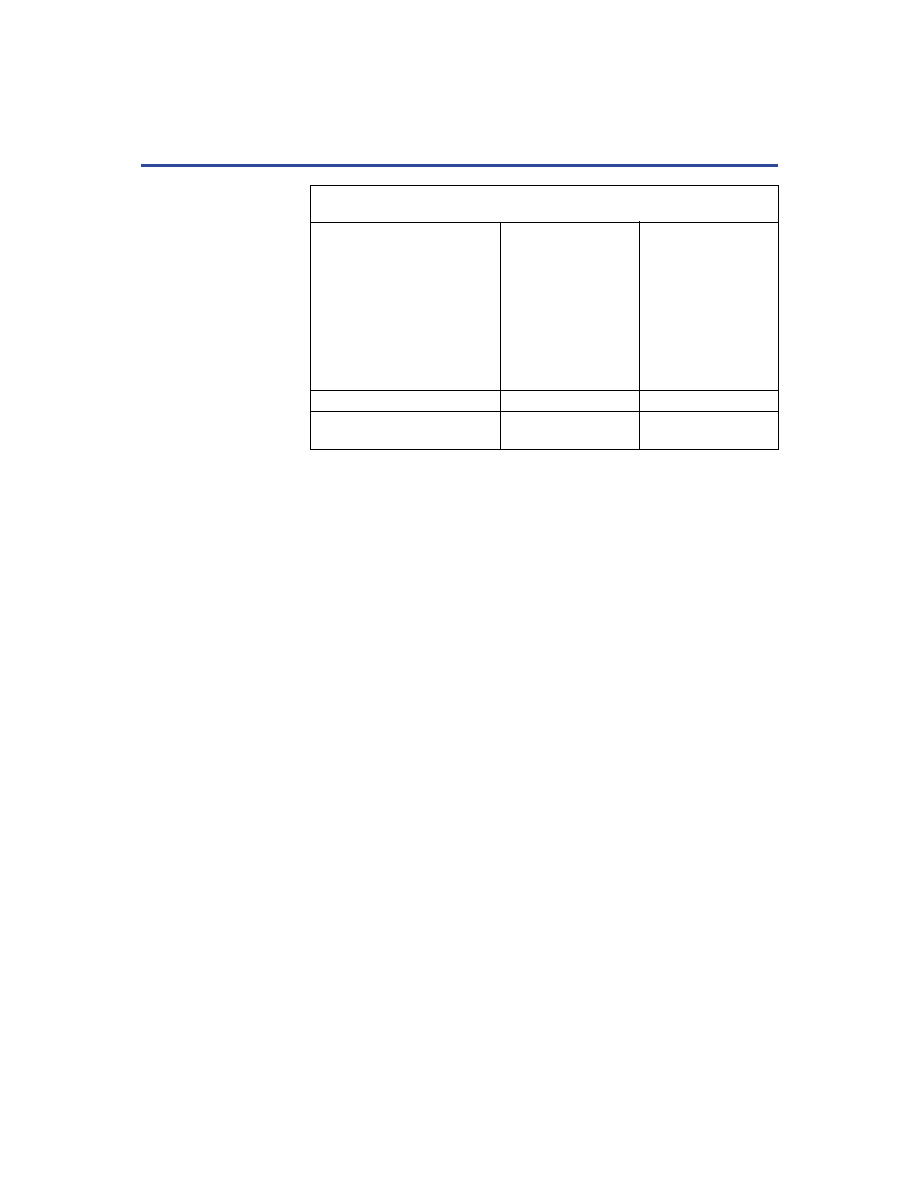

Table 2. APEX 20K Supply Voltages

Feature

EP20K100

EP20K200

EP20K400

EP20K60E

EP20K100E

EP20K160E

EP20K200E

EP20K300E

EP20K400E

EP20K600E

EP20K1000E

EP20K1500E

Internal supply voltage (VCCINT)

2.5 V

1.8 V

MultiVolt I/O interface voltage

levels (VCCIO)

2.5 V, 3.3 V

5.0 V (1)

1.8 V, 2.5 V, 3.3 V

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EP20K60EFC484 | LOADABLE PLD, PBGA484 |

| EP20K60EFC672-1 | LOADABLE PLD, PBGA672 |

| EP20K60EFC672-2 | LOADABLE PLD, PBGA672 |

| EP20K60EFC672-3 | LOADABLE PLD, PBGA672 |

| EP20K60EFC672 | LOADABLE PLD, PBGA672 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP20K60EFI144-1ES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

| EP20K60EFI144-2ES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

| EP20K60EFI144-3ES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

| EP20K60EFI324-1ES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

| EP20K60EFI324-2ES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。