- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄10240 > CS181002-CQZ (Cirrus Logic Inc)IC COBRANET CS181002 144LQFP PDF資料下載

參數(shù)資料

| 型號: | CS181002-CQZ |

| 廠商: | Cirrus Logic Inc |

| 文件頁數(shù): | 5/15頁 |

| 文件大小: | 0K |

| 描述: | IC COBRANET CS181002 144LQFP |

| 標準包裝: | 60 |

| 系列: | CobraNet® |

| 類型: | 音頻處理器 |

| 應用: | 網(wǎng)絡 |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 144-LQFP |

| 供應商設備封裝: | 144-LQFP(20x20) |

| 包裝: | 托盤 |

| 產(chǎn)品目錄頁面: | 758 (CN2011-ZH PDF) |

| 配用: | 598-1021-ND - MODULE COBRANET 4961 CM2 FB 598-1020-ND - MODULE COBRANET 1810 CM2 MT |

| 其它名稱: | 598-1024 |

CobraNet Hardware User’s Manual

Pinout and Signal Descriptions

DS651UM23

Copyright 2005 Cirrus Logic, Inc.

13

Version 2.3

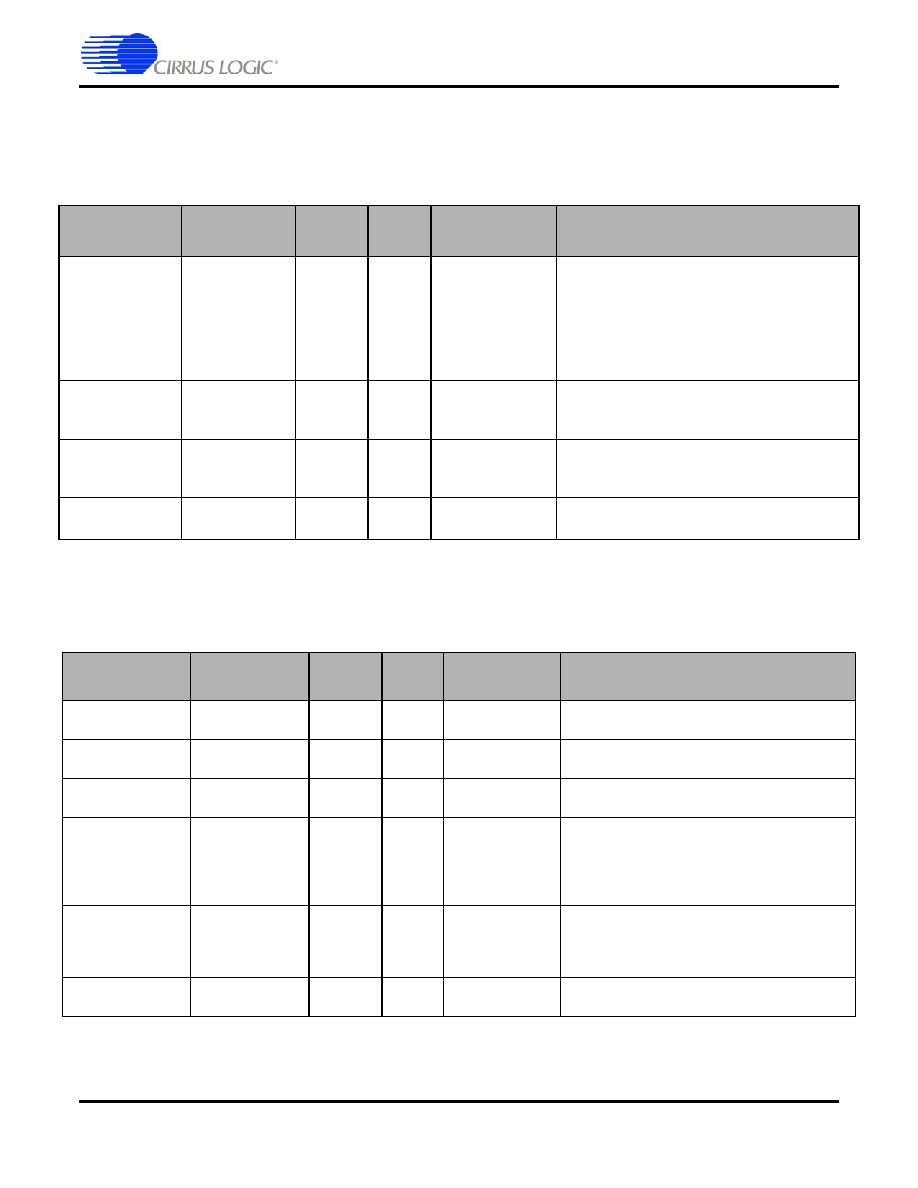

4.2.3 Synchronous Serial (Audio) Signals

The synchronous serial interfaces are used to bring digital audio into and out of the

system. Typically the synchronous serial is wired to ADCs and/or DACs. Detailed timing

and format is described in "Digital Audio Interface" on page 19.

4.2.4 Audio Clock Signals

See "Synchronization" on page 17 for an overview of synchronization modes and issues.

*An external multiplexor controlled by this pin is required for full MCLK_IN and MCLK out

implementation.

Signal

Description

Direction

CM-2

Pin #

CS1810xx/

CS4961xx Pin #

Notes

DAO1_SCLK

Audio Bit Clock

Out

J3:A7

20

Synchronous serial bit clock.

64 FS for CS18100x & CS49610x (2x1 channel)

64 FS for CS18101x & CS49611x (2x4

channels)

128 FS for CS18102x & CS49612x (4x4

channels)

Typically tied to DAI1_SCLK.

DAO1_DATA[3:0]

Audio Output

Data

Out

J3:A18,

B18

15-17, 19

Output synchronous serial audio data

DAO1_DATA[3:1] not used for CS18100x &

CS49610x.

DAI1_DATA[3:0]

Audio Input Data

In

J3:

A[15:12]

131, 132, 134, 135

Input synchronous serial audio data

DAI1_DATA[3:1] not used for CS18100x &

CS49610x.

DAI1_SCLK

Audio Bit Clock

In

J4:A7

137

Should be tied to DAO1_SCLK.

Synchronous serial bit clock.

Signal

Description

Direction

CM-2

Pin #

CS1810xx/

CS4961xx Pin #

Notes

DAI1_LRCLK

Sample clock

input

In

138

Should be tied to DAO1_LRCLK for all devices.

DAO1_LRCLK

(FS1)

Sample clock

output

Out

J3:A3

22

FS1 (word clock) for CS18100x/CS49610x and

CS18101x/CS49611x.

DAO2_LRCLK

(FS1)

Sample clock

output

Out

J3:A3

14

FS1 (word clock) for CS18102x & CS49612x.

REFCLK_IN

Reference clock

In

J3:A6

97

Clock input for synchronizing network to an

external clock source, for redundancy control

and synchronization of FS divider chain to

external source. See "Synchronization" on

page 17 for more detail.

MCLK_IN

Master audio

clock input

In

J3:A5

8*

For systems featuring multiple CobraNet

interfaces operating off a common master

clock. See "Synchronization" on page 17 for

more detail.

MCLK_OUT

Master audio

clock output

Out

J3:A4

8*

Low jitter 24.576 MHz master audio clock.

相關PDF資料 |

PDF描述 |

|---|---|

| VI-B6Z-MX | CONVERTER MOD DC/DC 2V 30W |

| VI-233-CU-F3 | CONVERTER MOD DC/DC 24V 200W |

| ADAU1442YSVZ-3A | IC SIGMADSP 28B 175MHZ 100TQFP |

| VI-B6Z-MW | CONVERTER MOD DC/DC 2V 40W |

| VI-233-CU-F1 | CONVERTER MOD DC/DC 24V 200W |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| CS181002-CQZ/A1 | 制造商:CIRRUS 制造商全稱:Cirrus Logic 功能描述:Digital Audio Networking Processor |

| CS181002-CQZR | 功能描述:音頻 DSP IC CobraNet Audio Networking Processor RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風格: 封裝 / 箱體: 封裝:Tube |

| CS181012-CQ | 功能描述:音頻 DSP IC CobraNet Audio Networking Processor RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風格: 封裝 / 箱體: 封裝:Tube |

| CS181012-CQ/A1 | 制造商:CIRRUS 制造商全稱:Cirrus Logic 功能描述:Digital Audio Networking Processor |

| CS181012-CQA1 | 制造商:Cirrus Logic 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。