- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄298913 > CAT24C03WI-T3 (ON SEMICONDUCTOR) 256 X 8 I2C/2-WIRE SERIAL EEPROM, PDSO8 PDF資料下載

參數(shù)資料

| 型號(hào): | CAT24C03WI-T3 |

| 廠商: | ON SEMICONDUCTOR |

| 元件分類: | PROM |

| 英文描述: | 256 X 8 I2C/2-WIRE SERIAL EEPROM, PDSO8 |

| 封裝: | 0.150 INCH, ROHS COMPLIANT, MS-012, SOIC-8 |

| 文件頁數(shù): | 8/14頁 |

| 文件大?。?/td> | 159K |

| 代理商: | CAT24C03WI-T3 |

CAT24C03, CAT24C05

http://onsemi.com

3

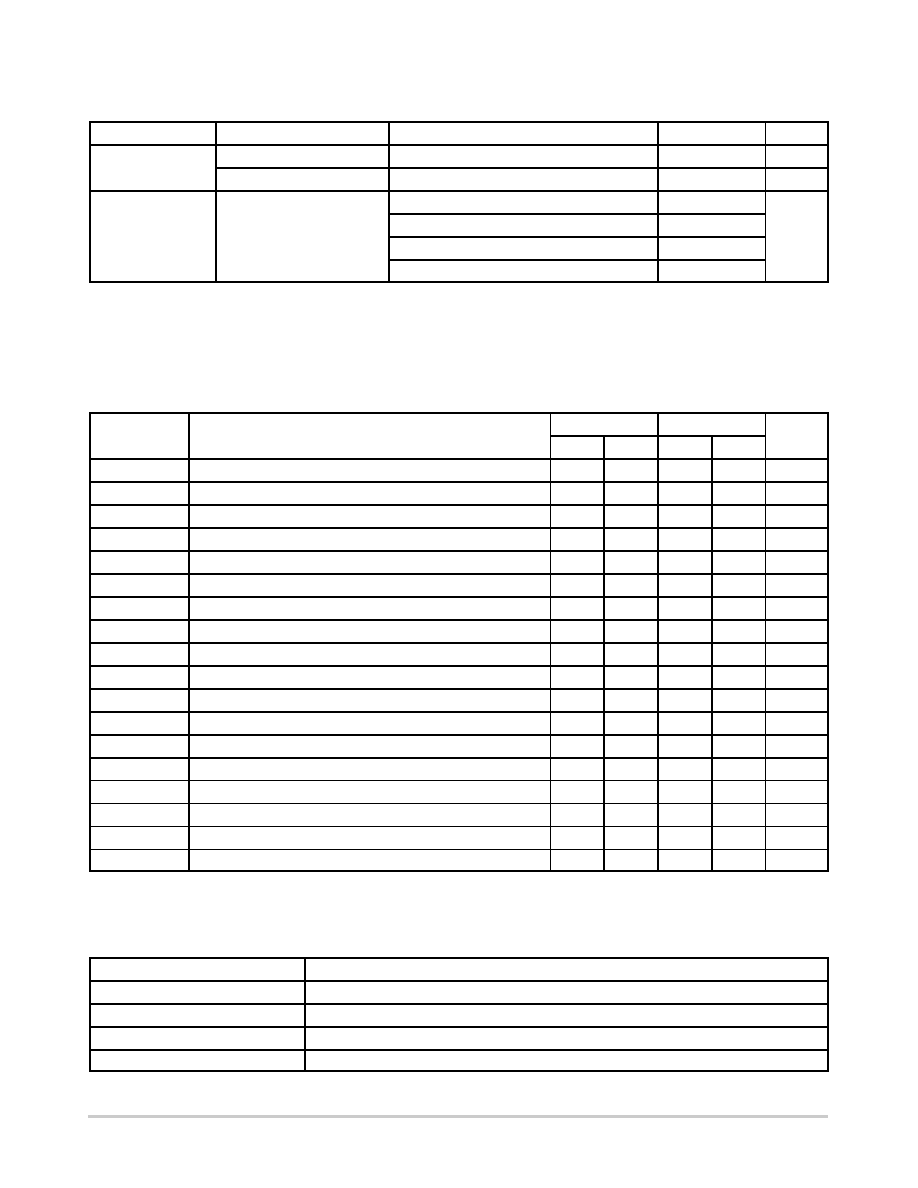

Table 4. PIN IMPEDANCE CHARACTERISTICS

(VCC = 1.8 V to 5.5 V, TA = 40°C to +85°C, unless otherwise specified.)

Symbol

Parameter

Conditions

Max

Units

SDA I/O Pin Capacitance

VIN = 0 V

8

pF

Input Capacitance (Other Pins)

VIN = 0 V

6

pF

WP Input Current

VIN < VIH, VCC = 5.5 V

200

mA

VIN < VIH, VCC = 3.3 V

150

VIN < VIH, VCC = 1.8 V

100

VIN > VIH

1

4. These parameters are tested initially and after a design or process change that affects the parameter according to appropriate AECQ100

and JEDEC test methods.

5. When not driven, the WP pin is pulled down to GND internally. For improved noise immunity, the internal pulldown is relatively strong;

therefore the external driver must be able to supply the pulldown current when attempting to drive the input HIGH. To conserve power, as

the input level exceeds the trip point of the CMOS input buffer (~ 0.5 x VCC), the strong pulldown reverts to a weak current source.

Table 5. A.C. CHARACTERISTICS

Symbol

Parameter

Standard

Fast

Units

Min

Max

Min

Max

FSCL

Clock Frequency

100

400

kHz

tHD:STA

START Condition Hold Time

4

0.6

ms

tLOW

Low Period of SCL Clock

4.7

1.3

ms

tHIGH

High Period of SCL Clock

4

0.6

ms

tSU:STA

START Condition Setup Time

4.7

0.6

ms

tHD:DAT

Data In Hold Time

0

ms

tSU:DAT

Data In Setup Time

250

100

ns

tR

SDA and SCL Rise Time

1000

300

ns

SDA and SCL Fall Time

300

ns

tSU:STO

STOP Condition Setup Time

4

0.6

ms

tBUF

Bus Free Time Between STOP and START

4.7

1.3

ms

tAA

SCL Low to Data Out Valid

3.5

0.9

ms

tDH

Data Out Hold Time

100

ns

Noise Pulse Filtered at SCL and SDA Inputs

100

ns

tSU:WP

WP Setup Time

0

ms

tHD:WP

WP Hold Time

2.5

ms

tWR

Write Cycle Time

5

ms

Powerup to Ready Mode

1

ms

6. Test conditions according to “A.C. Test Conditions” table.

7. Tested initially and after a design or process change that affects this parameter.

8. tPU is the delay between the time VCC is stable and the device is ready to accept commands.

Table 6. A.C. TEST CONDITIONS

Input Levels

0.2 x VCC to 0.8 x VCC

Input Rise and Fall Times

v 50 ns

Input Reference Levels

0.3 x VCC, 0.7 x VCC

Output Reference Levels

0.5 x VCC

Output Load

Current Source: IOL = 3 mA (VCC w 2.5 V); IOL = 1 mA (VCC < 2.5 V); CL = 100 pF

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CAT24C16ZJI | 2K X 8 I2C/2-WIRE SERIAL EEPROM, PDSO8 |

| CAT24WC128P-3 | 16K X 8 I2C/2-WIRE SERIAL EEPROM, PDIP8 |

| CAT25010UA-1.8 | EEPROM |

| CAT25010UE-1.8 | EEPROM |

| CAT25010UE-1.8TE13 | EEPROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CAT24C03YI-3 | 制造商:CATALYST 制造商全稱:Catalyst Semiconductor 功能描述:2-Kb and 4-Kb I2C Serial EEPROM with Partial Array Write Protection |

| CAT24C03YI-G | 功能描述:電可擦除可編程只讀存儲(chǔ)器 (256x8) 2K 1.8 - 5.5 Industrial Temp RoHS:否 制造商:Atmel 存儲(chǔ)容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| CAT24C03YI-G3 | 制造商:CATALYST 制造商全稱:Catalyst Semiconductor 功能描述:2-Kb and 4-Kb I2C Serial EEPROM with Partial Array Write Protection |

| CAT24C03YI-GT | 制造商:CATALYST 制造商全稱:Catalyst Semiconductor 功能描述:2-Kb and 4-Kb I2C Serial EEPROM with Partial Array Write Protection |

| CAT24C03YI-GT3 | 功能描述:電可擦除可編程只讀存儲(chǔ)器 2K-Bit I2C Serial 電可擦除可編程只讀存儲(chǔ)器 RoHS:否 制造商:Atmel 存儲(chǔ)容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。